# INSTITUTO POTOSINO DE INVESTIGACIÓN CIENTÍFICA Y TECNOLÓGICA, A.C.

### **POSGRADO EN CIENCIAS APLICADAS**

Compensación de potencia reactiva y distorsión armónica de la corriente de línea usando un filtro activo paralelo monofásico.

Tesis que presenta

Misael Francisco Martínez Montejano

Para obtener el grado de

Maestro en Ciencias Aplicadas

En la opción de

**Control y Sistemas Dinámicos**

Director de la Tesis:

Dr. Gerardo Escobar Valderrama

### Instituto Potosino de Investigación Científica y Tecnológica, A.C.

#### Acta de Examen de Grado

#### COPIA CERTIFICADA

El Secretario Académico del Instituto Potosino de Investigación Científica y Tecnológica, A.C., certifica que en el Acta 001 del Libro Primero de Actas de Exámenes de Grado del Programa de Maestría en Ciencias Aplicadas en la opción de Control y Sistemas Dinámicos está asentado lo siguiente:

En la ciudad de San Luis Potosí a los 25 días del mes de agosto del año 2004, se reunió a las 10:00 horas en las instalaciones del Instituto Potosino de Investigación Científica y Tecnológica, A.C., el Jurado integrado por:

Dr. Jesús Leyva Ramos Presidente IPICYT

Dr. Gerardo Escobar Valderrama Secretario IPICYT

Dr. Jorge Alberto Morales Saldaña Sinodal externo UASLP

a fin de efectuar el examen, que para obtener el Grado de:

MAESTRO EN CIENCIAS APLICADAS EN LA OPCIÓN DE CONTROL Y SISTEMAS DINÁMICOS

sustentó el C.

#### Misael Francisco Martínez Montejano

sobre la Tesis intitulada:

Compensación de potencia reactiva y distorsión armónica de la corriente de línea usando un filtro activo paralelo monofásico.

que se desarrolló bajo la dirección de

#### Dr. Gerardo Escobar Valderrama

El Jurado, después de deliberar, determinó

#### **APROBARLO**

Dándose por terminado el acto a las 12:00 horas, procediendo a la firma del Acta los integrantes del Jurado. Dando fé el Secretario Académico del Instituto.

A petición del interesado y para los fines que al mismo convengan, se extiende el presente documento en la ciudad de San Luis Potosí, S.L.P., México, a los 25 días del mes agosto de 2005.

Mtra. Ma. Elisa Lucio Aguilar

Jefa del Departamento de Asuntos Escolares

### INSTITUTO POTOSINO DE INVESTIGACIÓN CIENTÍFICA Y TECNOLÓGICA, A.C.

### DIVISIÓN DE MATEMÁTICAS APLICADAS Y SISTEMAS COMPUTACIONALES

MAESTRÍA EN CIENCIAS APLICADAS CON OPCIÓN EN CONTROL Y SISTEMAS DINÁMICOS

COMPENSACIÓN DE POTENCIA REACTIVA Y DISTORSIÓN ARMÓNICA DE LA CORRIENTE EN LA LÍNEA USANDO UN FILTRO ACTIVO PARALELO MONOFÁSICO

| _         | Ing. Misael Francisco Martínez Montejano         |

|-----------|--------------------------------------------------|

| SINODALES |                                                  |

|           |                                                  |

|           | Dr. Gerardo Escobar Valderrama (Asesor de Tesis) |

|           |                                                  |

|           | Dr. Jesús Leyva Ramos                            |

|           |                                                  |

|           | Dr. Jorge Alberto Morales Saldaña                |

A mis padres y hermanos, por su total apoyo, comprensión y muestras de cariño incondicional.

# AGRADECIMIENTOS

A mis padres por su apoyo cuando más lo necesitaba y por confiar plenamente en mí.

Al Dr. Gerardo Escobar V. por sus consejos, amistad y dirección brindada a lo largo de este proyecto.

A mis maestros Dr. Jesús Leyva, Dr. Hugo Cabrera, Dr. Haret Rosu, Dr. David Lizárraga, Dr. Arturo Zavala, Dr. Ricardo Femat por sus consejos y amistad.

A mis compañeros y amigos Michael, Vicente, Raúl, Octavio, Pánfilo, Sosa, Gabriel, Andrés, Rafa, Chen, Mario por su apoyo y amistad.

A mis amigos Israel, Rubén, Juan José, Néstor, Miguel, Alfredo, Mariana, Nashelli, Gaby, Cynthia, Rodolfo, Jorge Carlos, Omar, Vianney, Victor, Victor Mora, Irasema, Juan Manuel, Tello, Jonatan por su amistad.

Al programa de becas crédito de CONACYT por el financiamiento que proporcionaron para poder concluir este trabajo.

### **RESUMEN**

La calidad de la línea de alimentación de energía eléctrica se ve afectada por una serie de perturbaciones causadas, principalmente, por factores externos como lo son: fenómenos metereológicos, fallas al funcionamiento propio del sistema de distribución, y el funcionamiento de las cargas conectadas al sistema. El uso de estas cargas degrada la calidad de la energía utilizada, debido a la generación de armónicos, tanto de corriente como de voltaje, y demanda de potencia reactiva.

Ante esta situación, los filtros activos de potencia suponen una solución atractiva para los problemas relacionados con un excesivo contenido armónico en las líneas de alimentación, pues su estructura basada en un inversor de voltaje (VSI) permite, simultáneamente, la cancelación de corrientes armónicas y la corrección del factor de potencia.

Existen numerosas topologías para los filtros activos paralelos, en la presente tesis se muestra una topología que tiene la ventaja de manejar una sola rama de interruptores, pero presenta el problema de balancear el voltaje de los capacitores en el lado de corriente continua.

La tesis se compone de seis capítulos. En el Capítulo I se presenta la introducción al presente trabajo. En el Capitulo II se obtiene un modelo matemático para esta topología, en el cual las variables de estado representan las dinámicas de la corriente de línea, la suma del voltaje de los capacitores y la diferencia del voltaje de éstos. Además, se establecen los objetivos de control claramente con base en las variables de estado obtenidas.

Una vez establecidos los objetivos de control, en el Capítulo III se diseña una ley de control que permite cumplir estos objetivos. La ley de control propuesta es dividida en tres lazos de control, uno interno para garantizar seguimiento de corriente, y dos lazos de control externos que garantizan regulación y balance de voltajes en los capacitores. Esta propuesta está basada en ideas de pasividad, control adaptable e inversión parcial del sistema; además presenta la ventaja de no depender de los parámetros del sistema y de sólo

necesitar una medición de corriente (corriente de línea) y tres de voltaje (de línea y voltajes de capacitores). Finalmente se presentan en este capítulo algunos resultados de simulación.

Como parte fundamental de esta tesis se llevó a cabo la implementación física de un prototipo de pruebas de filtro activo con la topología mencionada. En el Capítulo IV se describe el diseño de la etapa de potencia, tarjetas de sensado y tarjetas de interfaz, así como también la programación de la ley de control en una tarjeta dSpace.

Los resultados experimentales aparecen en el Capítulo V. Estos resultados permiten comprobar que la ley de control propuesta alcanza los objetivos de control establecidos, tanto para seguimiento de corriente como para regulación y balance de voltajes en los capacitores.

La tesis termina con el Capítulo VI donde se enumeran algunas conclusiones, así como algunas actividades a futuro.

# ÍNDICE

| CAPITULO I INTRODUCCION                                                          | 1       |

|----------------------------------------------------------------------------------|---------|

| CAPÍTULO II PLANTEAMIENTO DEL PROBLEMA                                           | 5       |

| 2.1 MODELO MATEMÁTICO                                                            | 5       |

| 2.2 OBJETIVOS DE CONTROL                                                         | 8       |

| 2.3 SUPOSICIONES PRINCIPALES EN EL DESARROLLO DE LA LEY D<br>CONTROL             | )Е<br>9 |

| CAPÍTULO III DISEÑO Y RESULTADOS DE SIMULACIÓN DE LA LEY DI<br>CONTROL PROPUESTA | E<br>12 |

| 3.1 LEY DE CONTROL                                                               | 13      |

| 3.1.1 LAZO DE CONTROL INTERNO PARA SEGUIMIENTO DE CORRIENTE                      | 13      |

| 3.1.2 LAZO DE CONTROL EXTERNO PARA BALANCE DE CAPACITORES                        | 16      |

| 3.1.3 LAZO DE CONTROL EXTERNO PARA REGULACION                                    | 18      |

| 3.2 RESULTADOS DE SIMULACIÓN                                                     | 23      |

| CAPÍTULO IV DISEÑO DEL PROTOTIPO DE PRUEBAS                                      | 29      |

| 4.1 CARGA NO LINEAL                                                              | 30      |

| 4.2 ETAPA DE POTENCIA                                                            | 31      |

| REFERENCIAS                                           | 53 |

|-------------------------------------------------------|----|

| APÉNDICE A PUERTOS USADOS DE LA TARJETA dSPACE DS1103 | 50 |

| CAPÍTULO VI CONCLUSIONES Y TRABAJO A FUTURO           | 48 |

| CAPÍTULO V RESULTADOS EXPERIMENTALES                  | 41 |

| 4.4 TARJETA DE CONTROL                                | 35 |

| 4.3 TARJETAS DE SENSADO                               |    |

## CAPÍTULO I

# INTRODUCCIÓN

Sabemos que en nuestro país la demanda de electricidad por consumo habitacional crece día con día, al igual que la cantidad de cargas de tipo industrial. Máquinas eléctricas como soldadoras de arco, máquinas de inducción, fuentes basadas en rectificadores no controlados de potencia, aparatos electrodomésticos, computadoras, etc. son conectados día con día al sistema de distribución. El beneficio obtenido con el uso de estas cargas es indiscutible desde el punto de vista de control de procesos y viabilidad económica, pero su uso genera diversos problemas, entre los que se encuentran la degradación en la calidad de la energía utilizada, generación de armónicos, tanto de corriente como de voltaje y demanda de potencia reactiva. A esto podemos agregar las inevitables fallas en las líneas de transmisión, muchas veces causadas por factores externos como sobrecargas, negligencia y fenómenos meteorológicos.

Vemos así que se hace imperativa la búsqueda de soluciones alternativas que permitan aliviar los efectos negativos que una energía de baja calidad pudiera ocasionar, sobretodo en empresas donde existen delicados procesos industriales con cargas extremadamente sensibles, las cuales demandan una alta calidad de la energía suministrada.

Los problemas del sistema de potencia asociados con los armónicos comenzaron a ser de interés general en la década de los 70s. En un principio las compañías de distribución de energía y los consumidores industriales comenzaron a instalar capacitores para el mejoramiento del factor de potencia. Sin embargo, esta solución, además de limitada, puede provocar problemas de inestabilidad en la red de distribución. Por otra parte, el aumento en el uso de aparatos que no cuentan con técnicas de mitigación de armónicas, tanto en equipos de control industrial como en aplicaciones domésticas, combinado con el aumento en el uso de los capacitores para el mejoramiento del factor de potencia, crean un grave problema sobre el sistema de distribución eléctrico que tiene una capacidad limitada para absorber corrientes armónicas.

Debido a lo extenso de estos problemas, ha sido necesario desarrollar técnicas y lineamientos para la instalación de equipos y control de armónicos. Por ejemplo, las normas estadounidenses con respecto a los armónicos han sido agrupadas por la IEEE en la norma 519, la cual es básicamente un conjunto de recomendaciones para limitar la distorsión armónica inyectada a la red por el consumidor y la suministrada por la compañía de distribución.

Existen diversas propuestas de sistemas encaminados al mejoramiento de la calidad de la energía eléctrica los cuales han sido agrupados bajo el título de sistemas flexibles de transmisión de corriente alterna (FACTS) [4]. Entre estos destacan los filtros activos, cuya construcción se basa en los inversores de voltaje (VSI) que son dispositivos compuestos de ramas de interruptores conectados en serie y trabajando en forma complementaria. Dependiendo de la aplicación, estos interruptores pueden ser construidos con dispositivos MOSFET y Transistores Bipolares de Compuerta Aislada (IGBT), entre otros. La idea detrás de los filtros activos es que, controlando los estados de encendido y apagado de los interruptores, y auxiliados de filtros pasivos, es posible reconstruir señales periódicas destinadas a compensar la distorsión en las señales de interés.

Los filtros activos se clasifican a su vez en

- **1.-** Filtros activos en paralelo también conocidos como compensadores síncronos estáticos (STATCOM o D-STATCOM).

- **2.-** Filtros activos serie mejor conocidos comercialmente bajo el nombre de restauradores dinámicos de voltaje (DVR).

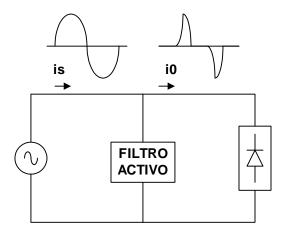

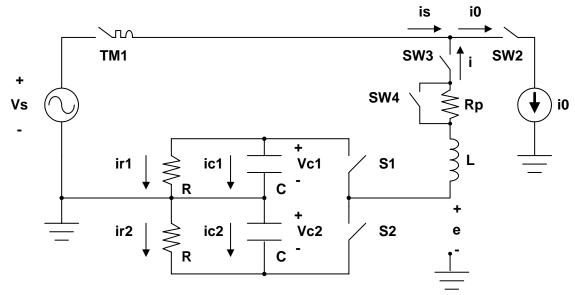

Fig. 1.1.- Filtro activo topología Paralelo.

Los filtros activos paralelos (ver Fig. 1.1) fueron concebidos con la idea de crear una fuente de corriente capaz de re-inyectar la parte distorsionante de la corriente de la carga desfasada 180°, de tal forma que al sumarse a la corriente de carga, la corriente total observada por la fuente sea lo mas "limpia" posible y este en fase con la señal de voltaje suministrado, logrando así un factor de potencia (PF) muy cercano a la unidad.

La aplicación de filtros activos en las líneas de distribución es todo un reto desde el punto de vista de control, ya que en el fondo se esta tratando con un problema de seguimiento o rechazo a perturbaciones periódicas. Algunas técnicas convencionales [1] usadas en filtros activos mostraron no alcanzar el desempeño deseable, como ya ha sido comentado en múltiples artículos, principalmente debido al limitado ancho de banda del controlador, a los retardos en la implementación digital y a la interacción entre carga y dinámica de la línea de alimentación [2]. La mayor parte de las leyes convencionales se limitan a diseñar la señal de referencia para la corriente a re-inyectar i(t), y aplican un control con altas ganancias, Modos Deslizantes (SMC) e incluso controladores Proporcional-Integral (PI), para intentar garantizar el seguimiento.

Fig. 1.2.- Topología de filtro activo paralelo propuesta.

En esta tesis se reporta la construcción de un prototipo para el filtro activo monofásico con la topología mostrada en la Fig. 1.2, para el cual, además, proponemos una ley de control novedosa. Esta topología presenta la ventaja de que utiliza únicamente dos

interruptores a diferencia de la topología con puente H completa donde se usan cuatro. Sin embargo, la aparición de dos capacitores en el lado de corriente continua (CD) complica el control, pues se tiene que garantizar, además del seguimiento de la referencia de corriente, que ambos capacitores alcancen el mismo voltaje constante deseado, esto es, que estén balanceados, o dicho de otra forma, que su suma tienda a una referencia constante y su diferencia tienda a cero.

Nuestra propuesta de control esta basada en las ideas de la teoría de pasividad (PBC) [6], control adaptable y la linealización por retroalimentación de estado. En especial, nuestro controlador compensa únicamente contra una cantidad seleccionada de componentes armónicos de la carga no lineal, la cual se supone es una perturbación periódica, esto es, nuestro controlador pertenece a la clase de compensadores selectivos [7], [9]. La observación interesante aquí es que, el controlador se reduce a un controlador muy similar al convencional al que se han añadido un banco de filtros resonantes, los cuales derivan de la aplicación de control adaptable, más un término de re-alimentación (feedforward) [8]. Cabe mencionar que este controlador garantiza el balance de los voltajes de los capacitores, gracias a la introducción de un grado de libertad extra. Este último modifica la señal de referencia de la corriente a inyectar, aunque solo transitoriamente, y se desvanece en el estado estacionario. A partir del prototipo construido fueron obtenidos algunos resultados experimentales que muestran el desempeño del controlador propuesto así como ventajas sobre el control convencional.

La presente tesis está integrada por seis capítulos:

#### I. Introducción.

- II. Planteamiento del problema: Se hace una breve descripción del sistema y se establece el modelo matemático, así también, se definen los objetivos de control.

- III. Diseño y Simulación de la Ley de Control Propuesta: Este capítulo está dedicado al desarrollo de la ley de control propuesta; muestra los resultados obtenidos en la simulación por computadora.

- *IV. Diseño del Prototipo de pruebas:* En este capítulo se muestran las características del prototipo de pruebas, la etapa de potencia, interfaces y la tarjeta de control usada; se incluyen las maniobras de operación y las protecciones que se implementaron.

- V. Resultados Experimentales: El último capítulo presenta los resultados experimentales obtenidos con el prototipo de pruebas en laboratorio.

#### VI. Conclusiones

# **CAPÍTULO II**

### PLANTEAMIENTO DEL PROBLEMA

En esta sección se plantea el modelo matemático de la topología propuesta para el filtro activo paralelo con el que se trabajó y se establecen los objetivos de control, así como las principales suposiciones que se hicieron para establecer la ley de control propuesta.

### 2.1.- MODELO MATEMÁTICO.

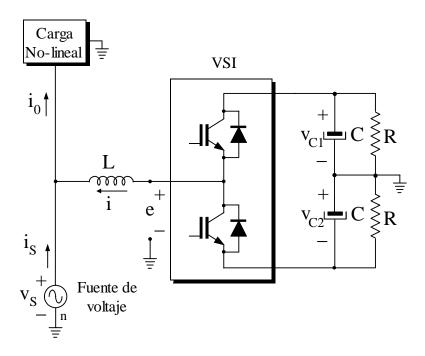

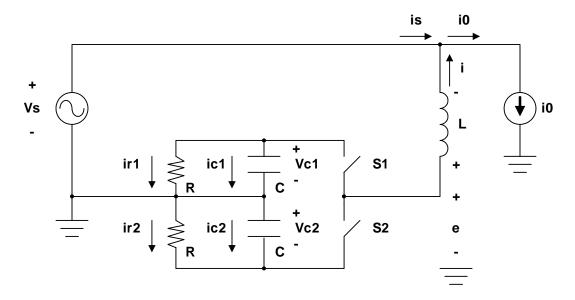

El esquema del filtro activo en paralelo usado se muestra en la Fig. 2.1. Este filtro está formado por un convertidor en configuración medio-puente, que a diferencia del convertidor de puente completo, consta de dos interruptores así como de dos capacitores cuya derivación central esta conectada a neutro. A grandes rasgos, los interruptores son controlados de forma tal que la corriente que atraviesa la red de alimentación sea lo más sinusoidal posible. Así también, este mismo control de los interruptores debe garantizar que ambos capacitores se mantengan cargados a un mismo nivel de voltaje determinado.

Fig. 2.1.- Esquemático del filtro activo paralelo.

Con base en el dibujo esquemático de la Fig. 2.1 se desarrolla el modelo matemático, donde

| и                      | entrada de control, $u \in \{0,1\}$                   |

|------------------------|-------------------------------------------------------|

| $V_{_S}$               | voltaje de línea                                      |

| $i_{_S}$               | corriente de línea                                    |

| $\dot{i}_0$            | corriente de carga                                    |

| i                      | corriente inyectada                                   |

| <i>S</i> 1, <i>S</i> 2 | posiciones de los interruptores                       |

| L                      | valor de la inductancia                               |

| R                      | valor de la resistencia de pérdidas                   |

| $i_{C1}, i_{C2}$       | corrientes que pasan por los capacitores              |

| $i_{r1}, i_{r2}$       | corrientes que pasan por las resistencias de pérdidas |

| e                      | voltaje inyectado a la bobina                         |

| $V_{C1}, V_{C2}$       | voltaje de los capacitores                            |

|                        |                                                       |

Es importante notar que en esta topología no se pueden tener ambos interruptores activos simultáneamente, ya que de darse esta condición causaría un cortocircuito entre las terminales de los condensadores, esto es, se debe forzar a que el trabajo de los interruptores sea complementario,  $S1 = \overline{S2}$ . Así mismo, se debe tener la precaución de introducir los correspondientes tiempos muertos entre el encendido y apagado de uno y otro interruptor.

Más aún, la topología usada exige que la tensión de cada condensador sea superior a la tensión máxima de la tensión de fase de red para garantizar un correcto funcionamiento, esto es,  $V_{C1}, V_{C2} > |V_S(t)| \ \ \forall t$ .

Analizando las dos posiciones de los interruptores tenemos los siguientes casos:

caso 1).- S1 encendido (S2 apagado): u = 1

$$\begin{split} i_{C1} &= -i - i_{r1} \\ i_{C2} &= 0 - i_{r2} \end{split} \qquad e = + V_{C1} \end{split}$$

caso 2).- S2 encendido (S1 apagado): u = 0

$$i_{C1} = 0 - i_{r1}$$

$$e = -V_{C2}$$

$$i_{C2} = i - i_{r2}$$

con base en lo anterior podemos escribir

$$i_{C1} = C \cdot \dot{V}_{C1} = -u \cdot i - \frac{V_{C1}}{R}$$

$$i_{C2} = C \cdot \dot{V}_{C2} = (1 - u) \cdot i - \frac{V_{C2}}{R}$$

$$e = u \cdot V_{C1} - (1 - u) \cdot V_{C2}$$

de donde tenemos que la dinámica de la corriente del inductor queda dada por

$$L \cdot \dot{i} = e - V_S = u \cdot (V_{C1} + V_{C2}) - V_{C2} - V_S$$

Para facilitar el manejo de las ecuaciones en lo que sigue es conveniente definir las siguientes variables de estado

$$x_1 \triangleq i_S$$

$$x_2 \triangleq V_{C1} + V_{C2}$$

$$x_3 \triangleq V_{C1} - V_{C2}$$

donde  $x_1$  representa la corriente de la línea,  $x_2$  representa la suma del voltaje de los capacitores y  $x_3$  la diferencia (el desbalance) de los voltajes de los capacitores.

Sabiendo que  $i_S = i_0 - i$  obtenemos la siguiente expresión para la dinámica de la corriente

$$L \cdot \dot{x}_1 = L \cdot \dot{\hat{i}_0} - (2 \cdot u - 1) \cdot \frac{x_2}{2} - \frac{x_3}{2} + V_S$$

(2.1)

De manera similar se obtienen las siguientes expresiones para las dinámicas de la suma y diferencia de los voltajes de los capacitores

$$C \cdot \dot{x}_2 = (2 \cdot u - 1) \cdot (x_1 - i_0) - \frac{x_2}{R}$$

(2.2)

$$C \cdot \dot{x}_3 = (x_1 - i_0) - \frac{x_3}{R} \tag{2.3}$$

En resumen, el modelo matemático de nuestra planta esta formado por las ecuaciones (2.1), (2.2) y (2.3).

#### 2.2.- OBJETIVOS DE CONTROL.

El objetivo de control consiste de los siguientes puntos:

1).- Seguimiento de corriente: Inyectar la corriente necesaria a través del filtro activo tal que, sumada a la corriente de carga, se observe en la terminal de la fuente de voltaje una señal de corriente proporcional a la señal de voltaje suministrado. En otras palabras, que las terminales de la fuente observen como carga total una simple resistencia. Matemáticamente, esto se puede escribir como

$$x_1 \rightarrow x_1^* = g \cdot Vs + \zeta$$

donde  $x_1^*$  representa la referencia de corriente y g es una variable escalar que representa la conductancia aparente, y por lo tanto en estado estacionario converge a una constante;  $\zeta$  representa un grado de libertad extra, introducido para garantizar el balance de los voltajes de los capacitores. Notar que  $\zeta$  modifica a la señal de referencia de la corriente de línea, pero como se verá mas adelante esta variable se desvanece en el estado estacionario. La forma de calcular a la variable g es también determinada más adelante. De hecho, debido a la selectividad de nuestro controlador, esta parte del objetivo de control se cumplirá únicamente para los componentes armónicos seleccionados. Con esto se busca que la

corriente de línea siga una referencia en fase con el voltaje de línea y mantenga la misma forma de onda que el voltaje.

2).- Regulación de tensión: Forzar a la suma de los voltajes de los capacitores, en promedio, a tomar un valor constante deseado en el estado estacionario<sup>1</sup>. Con esto se garantiza que existe suficiente energía almacenada en los capacitores para permitir el cumplimiento del objetivo anterior. Matemáticamente esto se representa de la siguiente manera

$$\langle x_2 \rangle_0 \to x_2^* = V_d$$

donde  $x_2^*$  representa la referencia de voltaje que en este caso se fija a una constante  $V_d$  y  $<\cdot>_0$  es usado para representar la componente de continua o promedio.

3).- Balance de los capacitores: Garantizar que ambos voltajes de los capacitores, en promedio, convergen al mismo valor constante, esto es,  $V_{\it d}$  / 2

$$\langle x_3 \rangle_0 \to x_3^* = 0$$

**Observación:** Cabe aclarar que los voltajes en los capacitores estarán contaminados por un pequeño rizo generado por la conmutación a alta frecuencia, así como de armónicos propagados desde la carga durante el proceso de compensación. Estos armónicos no se están compensando, ya que no es el objetivo principal de esta tesis, razón por la que sólo se consideran los valores promedio de la suma y la diferencia de los voltajes, esto es, las componentes de continua (CD).

# 2.3.- SUPOSICIONES PRINCIPALES EN EL DESARROLLO DE LA LEY DE CONTROL.

Para el correcto desarrollo e interpretación de la ley de control propuesta, son necesarias las siguientes suposiciones [16]:

**A1).-** Se considera que las señales de entrada son periódicas; y por lo tanto, se pueden representar en el dominio de la frecuencia de la siguiente manera:

$$V_S = \sum_{k \in H} \rho_k^T \ V_{S,k} \tag{2.4}$$

<sup>&</sup>lt;sup>1</sup> En este punto es más sencillo explicar el por qué se puede considerar a un filtro activo en paralelo también como un rectificador controlado, ya que se tiene como objetivo llevar la suma de los voltajes de los capacitores a un valor fijo, al menos en el estado estacionario.

$$i_0 = \sum_{k \in H} \rho_k^T \ I_{S,k} \tag{2.5}$$

$$V_{s,k} \triangleq \begin{pmatrix} a_k \\ b_k \end{pmatrix}, I_{s,k} \triangleq \begin{pmatrix} c_k \\ d_k \end{pmatrix}, \rho_k \triangleq \begin{pmatrix} \cos(k\omega t) \\ \sin(k\omega t) \end{pmatrix}, \forall k \in H$$

(2.6)

donde  $V_{s,k}$  e  $I_{s,k}$  representan los fasores de las señales de línea, y H representa un conjunto finito de los índices de componentes armónicos, esto es, suponemos que las señales de perturbación contienen un número finito de componentes armónicos, los cuales serán considerados para su compensación en la etapa de diseño de control. Más aún, de

aquí en adelante se usara únicamente  $\sum_{k}$  en lugar de  $\sum_{k \in H}$  para facilitar la notación.

Esta notación resulta muy conveniente para facilidad de manipulación de las expresiones matemáticas, tal como se muestra en el siguiente ejemplo, donde se calcula la derivada temporal de  $V_{\rm S}$ :

$$\dot{V}_S = \sum_{k=1}^{\infty} \dot{\rho}_k^T \ V_{S,k}$$

Desarrollando la derivada temporal del vector  $\rho_{\mathbf{k}}$  obtenemos

$$\dot{\rho}_{k} = \begin{pmatrix} -k\omega \cdot \sin(k\omega t) \\ k\omega \cdot \cos(k\omega t) \end{pmatrix} = k\omega J \rho_{k}$$

donde se ha definido a la matriz

$$J \triangleq \begin{pmatrix} 0 & -1 \\ 1 & 0 \end{pmatrix}$$

(2.7)

Esto resulta en la siguiente expresión, donde vemos que la derivada temporal es básicamente una rotación de la expresión original, multiplicada por unas constantes

$$\dot{V_S} = \sum_{k=1}^{\infty} k \,\omega \,\rho_k^T \,J \,V_{S,k}$$

De igual manera, se obtiene un resultado similar para la derivada temporal de la corriente  $i_0$

$$\dot{\hat{i}}_0 = \sum_{k=1}^{\infty} k \,\omega \,\rho_k^T \,J \,I_{S,k}$$

- **A2).-** La frecuencia de línea  $\omega$  es considerada como una constante conocida.

- **A3).-** Los fasores de línea  $V_{S,k}$ ,  $I_{S,k}$  y todos los parámetros del sistema (como R, L y C) son considerados como constantes desconocidas.

- **A4).-** Suposición de desacoplo: la dinámica de la corriente es suficientemente más rápida que las dinámicas de los voltajes de los capacitores [16].

# **CAPÍTULO III**

# DISEÑO Y RESULTADOS DE SIMULACIÓN DE LA LEY DE CONTROL PROPUESTA

En este capítulo se muestra el desarrollo de los lazos de control interno y externos en base al modelo matemático y a las suposiciones hechas en el capítulo anterior, se presenta el diagrama de bloques de la ley de control propuesta y los resultados obtenidos de la simulación por computadora en el programa MATLAB.

Es necesario hacer notar que la topología usada aquí no incluye ninguna fuente de poder externa para mantener los capacitores en el lado de CD del inversor de voltaje (VSI) cargados a un voltaje constante. En su lugar, el control estará formado por un lazo de control externo que permita la transferencia de energía del o para el capacitor por medio de la conmutación de los interruptores; y otro lazo de control externo que permita obtener el balance del voltaje de los capacitores. El lazo de control interno es diseñado para garantizar que la corriente inyectada siga a una forma de onda tal que, al sumarse con la corriente de carga, permitirá a que la corriente de línea siga a una referencia proporcional al voltaje de línea, y garantizar así un factor de potencia cercano a la unidad.

Un punto clave en el diseño del lazo de control interno es la reducción de las leyes adaptables a simples filtros resonantes, esto confirma el principio del modelo interno, así el banco de filtros resonantes representa el modelo de la perturbación a compensar, en este caso una perturbación periódica formada por componentes armónicos. Más aún, cabe

mencionar que nuestro método es selectivo, ya que solo compensará a un grupo de armónicos seleccionados. El diseño del control se basa en ideas de pasividad [6], control adaptable e inversión parcial del sistema.

#### 3.1.- LEY DE CONTROL.

Como se mencionó en el capítulo anterior, nuestra variable de control es **u**, pero para facilitar la manipulación de las ecuaciones en el diseño del controlador es conveniente definir la siguiente variable  $\Upsilon \triangleq (2 \cdot u - 1) \cdot x_2$  Sustituyendo la expresión anterior y haciendo los arreglos necesarios en las ecuaciones (2.1), (2.2) y (2.3) del capítulo anterior, se obtienen las siguientes expresiones para la dinámica de nuestra planta

$$L \cdot \dot{x}_1 = L \cdot \dot{\hat{i}_0} - \frac{\Upsilon}{2} - \frac{x_3}{2} + V_S \tag{3.1}$$

$$C \cdot \dot{z}_2 = (x_1 - i_0) \cdot \Upsilon - \frac{2 \cdot z_2}{R}$$

(3.2)

$$C \cdot \dot{x}_3 = (x_1 - i_0) - \frac{x_3}{R} \tag{3.3}$$

donde se ha definido  $z_2 \triangleq \frac{x_2^2}{2}$  en la expresión (3.2) para facilitar la notación.

#### 3.1.1.- LAZO DE CONTROL INTERNO PARA SEGUIMIENTO DE CORRIENTE.

El objetivo en esta etapa de diseño es garantizar el seguimiento de la señal  $x_1$  cuya dinámica esta dada por (3.1), hacia su referencia  $x_1^*$ . Escribiendo el modelo en términos del error

$$L \cdot \dot{\tilde{x}}_{1} = L \cdot \dot{\tilde{i}}_{0} - \frac{\Upsilon}{2} - \frac{x_{3}}{2} + V_{S} - L \cdot \dot{x}_{1}^{*}$$

(3.4)

donde  $\tilde{x}_1 \triangleq x_1 - x_1^*$  representa el error en la corriente respecto de su referencia.

Expresando  $\dot{x}_1^*$  e  $\dot{\hat{i}}_0$  en el dominio de la frecuencia, conforme a la suposición **A1** del capítulo anterior, usando la suposición de desacoplo **A3**, y reuniendo todos los términos en una sola sumatoria obtenemos la siguiente expresión:

$$L \cdot \dot{\tilde{x}}_{1} = -\frac{\Upsilon}{2} - \frac{x_{3}}{2} + V_{S} + \sum_{k} \rho_{k}^{T} \phi_{k}$$

(3.5)

donde hemos definido

$$\phi_k \triangleq Lk\omega J(I_{Sk} - gV_{Sk})$$

,  $\forall k \in H$

Observando el modelo de error (3.5), notamos que se trata de un sistema perturbado por la señal periódica desconocida  $V_S + \sum_k \rho_k^T \phi_k$ .

En el caso de que las perturbaciones y los parámetros fueran conocidos, se propondría la siguiente ley de control para el caso de parámetros conocidos

$$\Upsilon = 2 \cdot \left[ -\frac{x_3}{2} + V_S + \sum_k \rho_k^T \phi_k + k_1 \cdot \tilde{x}_1 \right]$$

(3.6)

Motivados por la estructura del controlador anterior, se propone la siguiente ley de control para el caso de parámetros desconocidos

$$\Upsilon = 2 \cdot \left[ -\frac{x_3}{2} + V_S + \sum_k \rho_k^T \hat{\phi}_k + k_1 \cdot \tilde{x}_1 \right]$$

(3.7)

donde  $\hat{\phi}_k$  representa el estimado del vector desconocido  $\phi_k$  y  $k_1$  es un parámetro de diseño que toma valores reales positivos.

El modelo de error en lazo cerrado con el controlador propuesto (3.7) toma la siguiente forma

$$L \cdot \dot{\tilde{x}}_1 = -k_1 \cdot \tilde{x}_1 - \sum_k \rho_k^T \tilde{\phi}_k \tag{3.8}$$

donde  $\tilde{\phi}_k \triangleq \hat{\phi}_k - \phi_k$ ,  $\forall k \in H$

Notamos que se trata de un sistema LTI perturbado por una señal periódica desconocida. Ahora, siguiendo el procedimiento de Lyapunov para encontrar las leyes de adaptación, proponemos la siguiente función de almacenamiento, la cual es una función cuadrática en término de los errores de corriente y paramétrico

$$V = \frac{L}{2} \cdot \tilde{x}_1^2 + \sum_k \frac{1}{\gamma_k} \tilde{\phi}_k^2 \tag{3.9}$$

derivando esta función a lo largo de la dinámica del error (3.8) se obtiene

$$\dot{V} = -k_1 \cdot \tilde{x}_1^2 - \tilde{x}_1 \cdot \sum_k \rho_k^T \tilde{\phi}_k + \sum_k \frac{1}{\gamma_k} \dot{\tilde{\phi}}_k^T \tilde{\phi}_k \tag{3.10}$$

Para cancelar los términos asociados al error paramétrico proponemos la siguiente ley de adaptación

$$\dot{\tilde{\phi}}_{k}^{T} = \gamma_{k} \cdot \tilde{x}_{1} \cdot \rho_{k}^{T} \quad , \quad \forall k \in H$$

(3.11)

donde  $\gamma_k$  ,  $\forall k \in H$  son parámetros de diseño, que toman valores constantes positivos.

Con esta ley de adaptación propuesta, la derivada de la función de almacenamiento se hace negativa semidefinida  $\dot{V} = -k_1 \cdot \tilde{x}_1^2$ .

De aquí se prueba que  $\tilde{x}_1 \to 0$  conforme  $t \to \infty$  asintóticamente. Más aún, siguiendo el Teorema de LaSalle [15],  $V \equiv 0 \Leftrightarrow \tilde{x}_1 \equiv 0$ , lo cual implica que  $\dot{\tilde{\phi}}_k = 0 \Rightarrow \tilde{\phi}_k = cte$ . Ahora bien, como tenemos que  $L \cdot \dot{\tilde{x}}_1 = -k_1 \cdot \tilde{x}_1 - \sum_k \rho_k^T \tilde{\phi}_k$  esto implica que  $\sum_k \rho_k^T \tilde{\phi}_k = 0 \Leftrightarrow \tilde{\phi}_k = 0$  de donde se concluye la convergencia de los parámetros a sus valores verdaderos.

Note que, dado que  $\phi_k = cte., \forall k \in H$ , entonces (3.11) también se puede escribir como

$$\dot{\hat{\phi}}_k = \gamma_k \cdot \rho_k \cdot \tilde{x}_1 \tag{3.12}$$

El problema de seguimiento de corriente queda entonces resuelto por el controlador formado por las expresiones (3.7) y (3.11). La expresión (3.11) es sin embargo difícil de implementar, dado que requiere el cálculo del vector  $\rho_k$  cuyos componentes son señales senoidales. Para reducir la complejidad de este controlador definimos las siguientes transformaciones, las cuales como se puede apreciar son simples rotaciones

$$\psi_k^r \triangleq \rho_k^T \, \hat{\phi}_k \tag{3.13}$$

$$\psi_k^i \triangleq \rho_k^T J \,\hat{\phi}_k \tag{3.14}$$

donde la matriz  $J \triangleq \begin{pmatrix} 0 & -1 \\ 1 & 0 \end{pmatrix}$  es una matriz antisimétrica que ya había sido definida en el capítulo anterior. De esta forma obtenemos la siguiente expresión final para la ley de control propuesta

$$\Upsilon = 2 \cdot \left[ -\frac{x_3}{2} + V_S + \sum_{k} \psi_k^r + k_1 \cdot \tilde{x}_1 \right]$$

(3.15)

$$\psi_k^r = \frac{\gamma_k \cdot s}{s^2 + (k\omega)^2} \cdot \tilde{x}_1 \quad , \quad \forall k \in H$$

(3.16)

Observamos que en esta última expresión, la parte dinámica correspondiente a la ley de adaptación, ha sido sustituida por un banco de filtros resonantes. Esto corrobora el *Principio del Modelo Interno* ya que los modelos correspondientes a las perturbaciones, en este caso componentes armónicas, son osciladores armónicos, esto es, filtros resonantes, los cuales tendrían que incluirse en el lazo de control a fin de garantizar el rechazo a dichas perturbaciones. Se observa también la naturaleza selectiva de nuestro controlador, ya que tenemos la libertad de seleccionar que componentes armónicos serán compensados, esto es, para compensar un determinado componente armónico se introduce un filtro resonante sintonizado a la frecuencia correspondiente, y se incluirán tantos filtros resonantes como componentes armónicos a compensar.

#### 3.1.2.- LAZO DE CONTROL EXTERNO PARA BALANCE DE CAPACITORES.

En esta segunda etapa diseñamos el lazo de control externo que se ocupa de garantizar el balance de los capacitores, gracias a la suposición de desacoplo podemos considerar que la corriente de línea  $x_1$  ya ha alcanzado a su referencia  $x_1^*$  en un tiempo relativamente pequeño y por lo tanto

$$x_1 = x_1^* = g \cdot V_S - \zeta \tag{3.17}$$

Para ver la necesidad de la introducción del grado de libertad extra  $\zeta$ , supongamos que la corriente de referencia únicamente incluye un término proporcional al voltaje de la fuente, esto es, considerando

$$x_1 = x_1^* = g \cdot V_S$$

entonces de (3.3), tendríamos que

$$C \cdot \dot{x}_3 = g \cdot V_S - i_0 - \frac{x_3}{R}$$

y considerando únicamente el promedio, esto es, extrayendo su componente de CD, nos queda

$$< C \cdot \dot{x}_3>_0 = < g \cdot V_S>_0 - < i_0>_0 - \frac{1}{R} \cdot < x_3>_0$$

y por lo tanto esto se reduce a

$$C\dot{x}_{30} = -\frac{x_{30}}{R}$$

donde  $x_{30} \triangleq \langle x_3 \rangle_0$  es la componente de CD de la variable  $x_3$ .

De la expresión anterior se puede apreciar que la velocidad de convergencia a cero de la diferencia de voltajes  $x_3$ , esto es, del balance, es muy lenta pues depende de la constante de tiempo RC, donde la resistencia R asociada a pérdidas tiene generalmente un valor muy grande. Esto explica la necesidad de incluir las resistencias de ecualización normalmente usadas por los diseñadores. Las cuales tienen el inconveniente de disipar mucha potencia haciendo el proceso menos eficiente. Para resolver este inconveniente, nosotros proponemos simular el funcionamiento de dichas resistencias a nivel de la ley de control, y para esto se incluye un grado de libertad extra. Este grado de libertad nos permitirá, además, controlar la velocidad de convergencia de dicha diferencia de voltajes a cero, esto es, la velocidad de balance de los capacitores. Este grado de libertad se incluye en la referencia de la corriente, como se mostró anteriormente, esto es,

$$x_1^* = g \cdot V_S - \zeta \tag{3.18}$$

Es claro que este grado de libertad distorsionará a la referencia de corriente de línea, sin embargo, como se verá mas adelante, se procurará encontrar una función que de preferencia actúe durante el transitorio y que se desvanezca en el estado estacionario.

Aplicando (3.17) en (3.3) y extrayendo la componente de DC se obtiene

$$< C \cdot \dot{x}_3>_0 = < g \cdot V_S>_0 - < i_0>_0 - \frac{1}{R} \cdot < x_3>_0 + < \zeta>_0$$

la cual se reduce a

$$C \cdot \dot{x}_{30} = <\zeta>_0 - \frac{1}{R} \cdot x_{30}$$

donde  $x_{30} = \langle x_3 \rangle_0$ .

Observando la forma del sistema anterior proponemos como función  $\zeta$

$$\zeta = -k_d \cdot \eta = -k_d \cdot \frac{x_3}{s+d}$$

donde vemos que  $\dot{\eta} = -d \cdot \eta + x_3$

y de esta forma

$$C \cdot \dot{x}_{30} = -k_d \cdot \eta_0 - \frac{1}{R} \cdot x_{3_0}$$

$$\dot{\eta}_0 = -d \cdot \eta_0 + x_{30}$$

El cual resulta ser un sistema LTI estable ya que la matriz

$$A = \begin{pmatrix} -\frac{1}{R} & -k_d \\ 1 & -d \end{pmatrix}$$

es Hurwitz para  $k_d > 0$ , d > 0. El parámetro R es siempre positivo, ya que corresponde al valor real de la resistencia de pérdidas.

En resumen, el controlador para el balance del voltaje de los capacitores esta dado por

$$x_1 \to x_1^* = g \cdot V_S - k_d \cdot \eta , g, k_d \in \mathbb{R}_+$$

(3.19)

$$\dot{\eta} = -d \cdot \eta + x_3 \quad , \quad d \in \mathbb{R}_+ \tag{3.20}$$

#### 3.1.3.- LAZO DE CONTROL EXTERNO PARA REGULACION.

En esta tercera etapa el diseño del control está encaminado a garantizar la regulación de la suma del voltaje de los capacitores, en otras palabras, mantener los capacitores cargados a un voltaje constante tal que permita el óptimo funcionamiento del filtro, y en especial, asegurar que el objetivo de seguimiento se cumpla correctamente. Nuevamente, usando la suposición de desacoplo, podemos considerar que la corriente de línea ya ha alcanzado a su referencia, y además los parámetros estimados han convergido a su valor verdadero, esto es

$$x_1 = x_1^* = g \cdot V_S - k_d \cdot \eta \tag{3.21}$$

$$\phi_k = \hat{\phi}_k \qquad , \quad \forall k \in H \tag{3.22}$$

donde hemos incluido ya el termino del grado de libertad extra en (3.21), el cual fue diseñado en el lazo de control externo anterior.

El controlador del lazo interno, en este caso se reduce a

$$\Upsilon = -x_3 + 2 \cdot V_S + 2 \cdot \sum_k \psi_k^r$$

donde  $\psi_k^r = \rho_k^T \phi_k = L \cdot \dot{i}_0 - L \cdot \dot{x}_1^*$ , que sustituida en la ley de control anterior resulta

$$\Upsilon = -x_3 + 2 \cdot V_S + 2 \cdot L \cdot \frac{d(i_0 - x_1^*)}{dx}$$

Sustituyendo esta expresión del controlador en el subsistema (3.2), que corresponde a la dinámica del cuadrado de la suma de los voltajes de los capacitores, obtenemos

$$C \cdot \dot{z}_{2} = 2 \cdot V_{S} \cdot x_{1}^{*} - 2 \cdot V_{S} \cdot i_{0} + x_{3} \cdot i_{0} - x_{3} \cdot x_{1}^{*} - 2 \cdot L \cdot \dot{\varepsilon} \cdot \varepsilon - \frac{2 \cdot z_{2}}{R}$$

(3.23)

donde se define  $\varepsilon \triangleq i_0 - x_1^*$ .

Extraemos ahora la componente de CD de la expresión (3.23) quedando

$$< C \cdot \dot{z}_2>_0 = < 2 \cdot V_S \cdot x_1^*>_0 - < 2 \cdot V_S \cdot i_0>_0 + < x_3 \cdot i_0>_0 - < x_3 \cdot x_1^*>_0 - 2 \cdot L \cdot < \dot{\varepsilon} \cdot \varepsilon>_0 - \frac{2}{R} \cdot < z_2>_0$$

Sustituyendo la expresión para la referencia de corriente (3.21), y realizando las reducciones pertinentes llegamos a

$$C \cdot \dot{z}_{20} = 2 \cdot g < V_S^2 >_0 -2 \cdot < V_S \cdot i_0 >_0 -k_d \cdot < x_3 \cdot \eta >_0 -\frac{2}{R} \cdot z_{20}$$

donde  $z_{20} = \langle z_2 \rangle_0$ .

Para reducir la notación de la expresión anterior consideremos las siguientes definiciones

$$\langle V_S^2 \rangle_0 \triangleq \frac{1}{T} \int_{t-T}^{\tau} V_S^2 dt = V_{Srms}^2$$

(3.24)

$$\langle V_{\varsigma} \cdot i_0 \rangle_0 \triangleq P_0 \tag{3.25}$$

donde la componente de CD de la dinámica del cuadrado de la suma del voltaje de los capacitores se reduce a

$$C \cdot \dot{z}_{20} = 2 \cdot g V_{Srms}^2 - 2P_0 - k_d \cdot \langle x_3 \cdot \eta \rangle_0 - \frac{2}{R} \cdot z_{20}$$

(3.26)

Este sistema es un sistema LTI perturbado por constantes desconocidas más el término  $k_d \cdot \langle x_3 \cdot \eta \rangle_0$  que se desvanece en estado estacionario, dado que  $x_3$  se desvanece. En este sistema la señal la variable g actúa como la entrada de control, y dado el tipo de sistema y perturbaciones proponemos el siguiente control

$$g = -k_p \cdot \chi - k_i \cdot \xi \tag{3.27}$$

$$\dot{\chi} = -k_b \cdot \chi + \tilde{z}_2 \tag{3.28}$$

$$\dot{\xi} = \tilde{z}_2 \tag{3.29}$$

donde  $k_p$ ,  $k_i$  y  $k_b$  son parámetros de diseño y definimos  $\tilde{z}_2 = \frac{x_2^2 - V_d^2}{2}$

El sistema de lazo cerrado, usando la expresión de g en (3.26), resulta en el siguiente modelo de error

$$\dot{\tilde{z}}_{20} = -\frac{2}{RC} \cdot \tilde{z}_{20} - \frac{2}{C} \cdot k_p \cdot V_{Srms}^2 \cdot \chi - \frac{2}{C} \cdot k_i \cdot V_{Srms}^2 \cdot \tilde{\xi}$$

$$\dot{\chi} = -k_h \cdot \chi + \tilde{z}_2$$

$$\dot{\tilde{\xi}} = \tilde{z}_2$$

donde

$$\tilde{\xi} \triangleq \xi - \overline{\xi}$$

, con  $\overline{\xi} = -\frac{1}{2k_i V_{\text{source}}^2} \left( \frac{V_d^2}{R} + 2P_0 \right)$ .

Este sistema resulta estable ya que la matriz

$$A' = \begin{pmatrix} 0 & -\frac{2}{C} \cdot k_p \cdot V_{Srms}^2 & -\frac{2}{C} \cdot k_i \cdot V_{Srms}^2 \\ 1 & -k_b & 0 \\ 1 & 0 & 0 \end{pmatrix}$$

es Hurwitz para  $k_p > 0$ ,  $k_i > 0$  y  $k_b > 0$ . El parámetro C es siempre positivo, ya que corresponde al valor real de la capacitancia.

En conclusión, la expresión matemática total para el control esta dada por las siguientes ecuaciones

i) Lazo interno (seguimiento de corriente)

$$u = \frac{1}{2} \cdot \left(\frac{\Upsilon}{2} + 1\right)$$

$$\Upsilon = -x_3 + 2 \cdot V_S + k_1 \cdot \tilde{x}_1 + \sum_k \psi_k^r$$

$$\psi_k^r = \frac{\gamma_k \cdot s}{s^2 + (k \cdot \omega)^2} \cdot \tilde{x}_1$$

donde

$$\tilde{x}_1 = x_1 - x_1^*$$

ii) Lazo externo (balance de capacitores)

$$x_1^* = g \cdot V_S - k_d \cdot \eta$$

$$\dot{\eta} = -d \cdot \eta + x_3$$

iii) Lazo externo (regulación de voltaje de los capacitores)

$$g = -k_n \cdot \chi - k_i \cdot \xi$$

$$\dot{\chi} = -k_b \cdot \chi + \tilde{z}_2$$

$$\dot{\xi} = \tilde{z}_2$$

donde

$$\tilde{z}_2 = \frac{x_2^2 - V_d^2}{2}$$

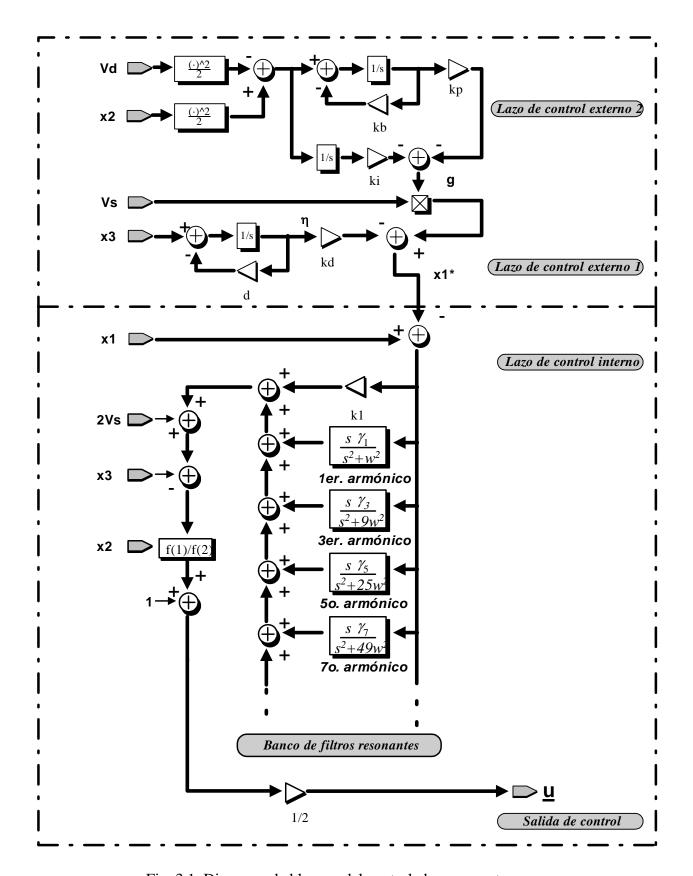

La Fig. 3.1. muestra el diagrama de bloques del controlador propuesto, donde se pueden apreciar los tres lazos de control. Nótese en el lazo de control interno la aparición del banco de filtros resonantes, lo que nos permite compensar la distorsión armónica en la corriente de línea.

Fig. 3.1. Diagrama de bloques del controlador propuesto

### 3.2.- RESULTADOS DE SIMULACIÓN.

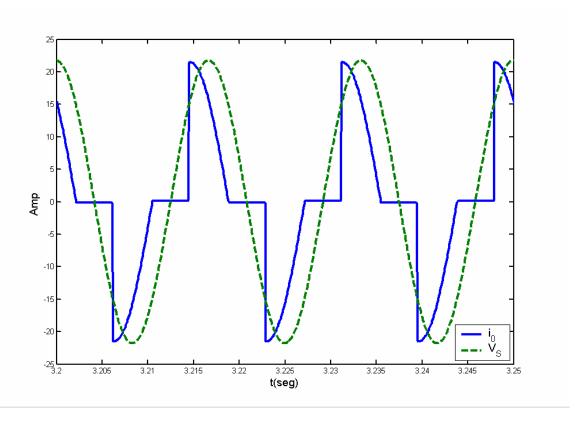

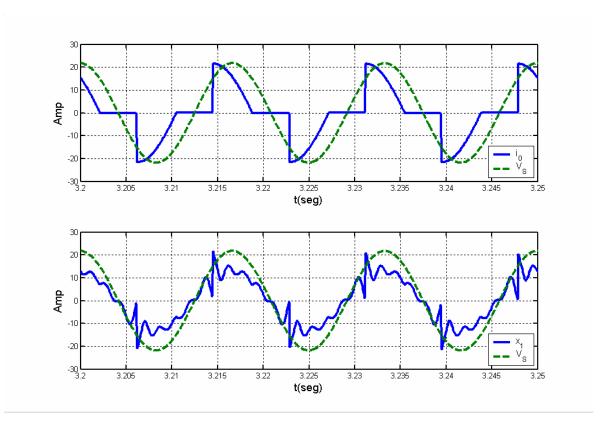

Las simulaciones de la ley de control propuesta se realizaron con el programa SIMULINK/MATLAB 6.5. Las condiciones iniciales y los parámetros del sistema se trataron de apegar lo más posible a los parámetros reales del sistema, esto es,  $x_3(0) = 0$  V y  $x_2(0) = 320$  V, es decir, se supone que ambos capacitores están cargados inicialmente con 160 V cada uno, y para la corriente  $x_1(0) = 0$ . Suponemos condiciones iniciales nulas para los estados del controlador. Se trabajó con la línea monofásica de 127 Vrms puramente sinusoidal, y se construyo una corriente de carga debida a un rectificador no controlado de diodos como se muestra en la Fig. 3.2.

Fig 3.2.- Formas de onda del voltaje de alimentación y la corriente de carga.

Estas mismas señales de entrada se muestran en la Fig. 3.3 junto con la gráfica de su espectro en frecuencia exhibiendo su contenido armónico. En esta figura, las barras en negro representan a los armónicos de la señal de corriente, cabe destacar que esta señal posee todos los armónicos impares.

Fig. 3.3.- Señales de entrada: (**ARRIBA**) formas de onda en el dominio del tiempo y (**ABAJO**) espectro en frecuencia mostrando el correspondiente contenido armónico.

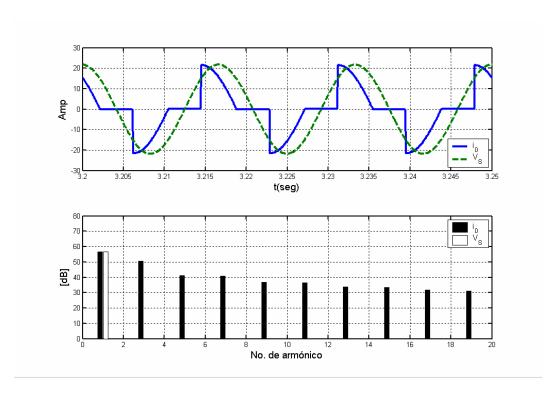

Fig. 3.4.- (**ARRIBA**) Señal de corriente de carga  $i_0$  y corriente de línea  $x_1 = i_S$  donde se han compensado los componentes armónicos 1, 3, 5, 7 y 9. (**ABAJO**) El correspondiente espectro en frecuencia mostrando el contenido armónico.

En la Fig. 3.4 se muestran las señales de corriente de carga y de línea. En esta última, para efectos de simulación, se escogió compensar únicamente los armónicos 1, 3, 5, 7 y 9. Se observa en la grafica de los espectros de frecuencia que en la corriente de línea los componentes armónicos compensados son considerablemente inferiores con respecto a los correspondientes componentes armónicos de la corriente de carga. Sin embargo, se aprecia un ligero incremento en los componentes armónicos superiores que no han sido tratados, para aliviar este problema se podrían incorporar más filtros resonantes.

En la Fig. 3.5 se muestran las señales de corriente de carga y de línea (ya compensada) comparadas con la forma senoidal del voltaje de la fuente (o de línea), esto con el fin de mostrar que esta última esta en fase con el voltaje de la fuente y se acerca más a una forma sinusoidal. La distorsión observada en la corriente de línea podría ser aún más reducida al incorporar más filtros resonantes para los armónicos de orden superior.

Fig. 3.5.- Señales de corriente de carga (**ARRIBA**) y de línea ya compensada (**ABAJO**) comparadas con la forma senoidal escalada del voltaje de la fuente (línea punteada).

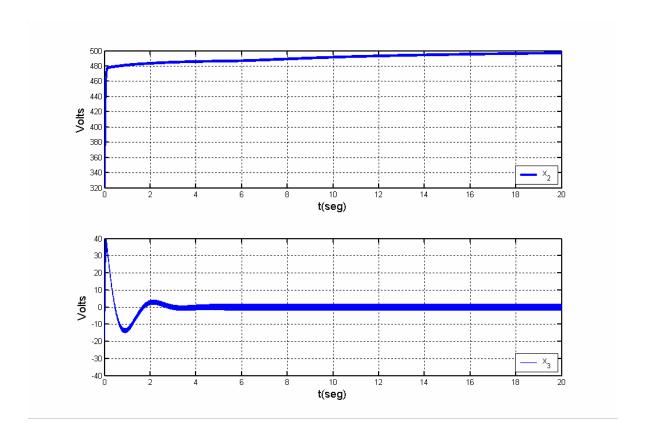

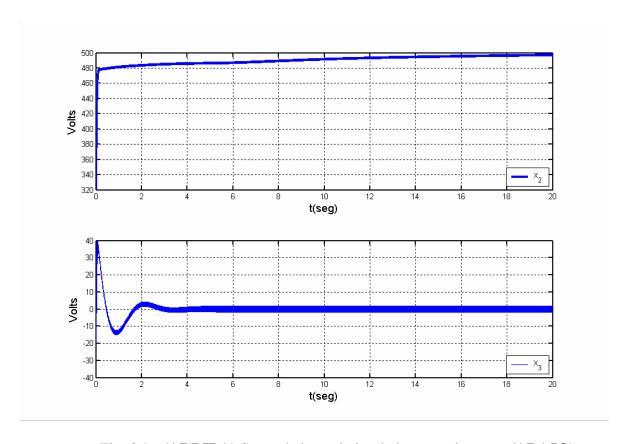

Las gráficas para la suma de voltajes de los capacitores y para el desbalance (diferencia) de los mismos se muestran en la Fig. 3.6. La suma de los voltajes tiene como condición inicial 320 V, mientras que la diferencia tiene condición inicial nula.

Fig. 3.6.- (**ARRIBA**) Suma de los voltajes de los capacitores, y (**ABAJO**) diferencia (desbalance) de los voltajes de los capacitores.

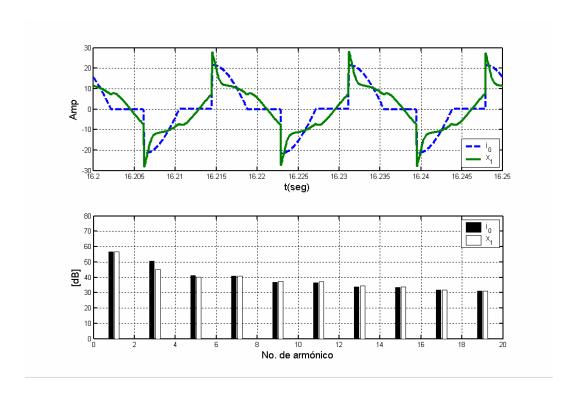

Las siguientes gráficas corresponden a la respuesta que tendría el filtro activo con un control convencional (un control con base proporcional-integral PI) en el lazo de control interno. Las ganancias y las señales de entrada son las mismas que con la ley de control propuesta para permitir una correcta comparación de ambas leyes de control.

Se presentan tanto las formas de onda de entrada y respuesta, así como el contenido armónico de las señales. También se presenta la respuesta que tiene con respecto a la suma y desbalance del voltaje de los capacitores.

Fig. 3.7.- (**ARRIBA**) Señal de corriente de carga  $i_0$  y corriente de línea  $x_I = i_S$  (**ABAJO**) El correspondiente espectro en frecuencia mostrando el contenido armónico.

Fig. 3.8.- Señal de corriente comparada con el voltaje de línea.

Fig. 3.9.- (**ARRIBA**) Suma de los voltajes de los capacitores, y (**ABAJO**) diferencia (desbalance) de los voltajes de los capacitores.

## **CAPÍTULO IV**

## DISEÑO DEL PROTOTIPO DE PRUEBAS

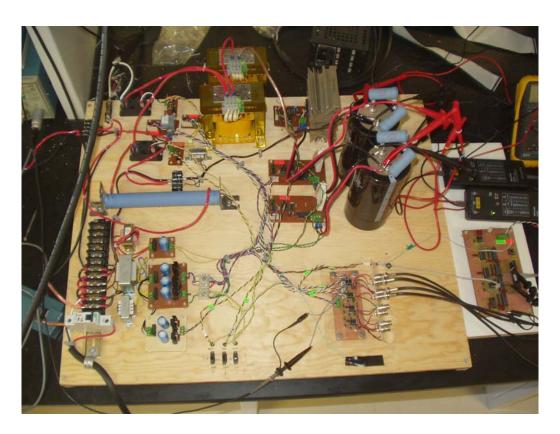

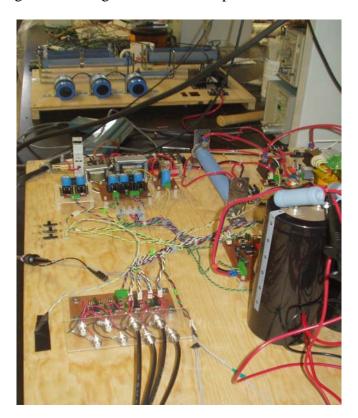

En este capítulo se muestra las características del prototipo que se construyó para probar la ley de control propuesta: la etapa de potencia y la carga no lineal, instrumentación electrónica, interfaces, características de la tarjeta de control y las maniobras de operación.

El diseño del prototipo de pruebas es una de las partes fundamentales de la presente tesis. Esta etapa establece necesidades que no se presentan en el diseño teórico ni en las simulaciones por computadora, las cuales deben de ser resueltas en el diseño del hardware. Por ejemplo, un dispositivo de potencia ideal no debería presentar limitaciones de conmutación, en términos de tiempo de activación y desactivación, sin embargo, en la realidad se presentan estos y más problemas.

La implementación del filtro activo propuesto requiere de la conmutación de dispositivos semiconductores con un rango de frecuencia de varias decenas de Kilo-Hertz (KHz). Para esto se utilizaron MOSFETs de potencia, los cuales están disponibles para aplicaciones de relativamente poca potencia, esto es, en el rango de 1000V, 50 A [17]. Fue necesario también diseñar los sensores utilizados para medir voltaje y corriente, así como las interfaces y protecciones necesarias para su conexión con la tarjeta de control.

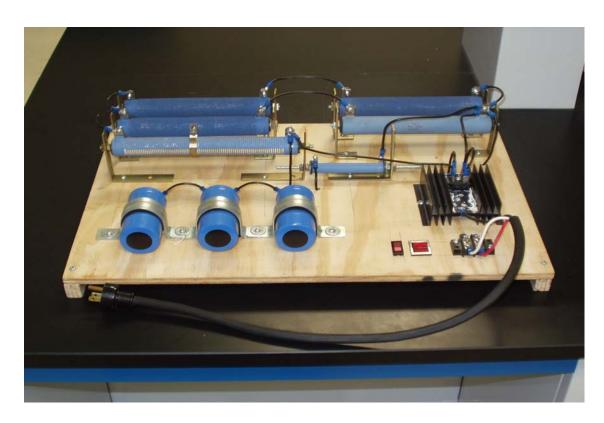

Como punto de partida consideremos que el prototipo fue diseñado para trabajar con una sola fase de 127 Vrms, que es considerada como la fuente de voltaje, a la cual se ha conectado una carga no lineal cuyo orden de potencia es de aproximadamente 2 kW.

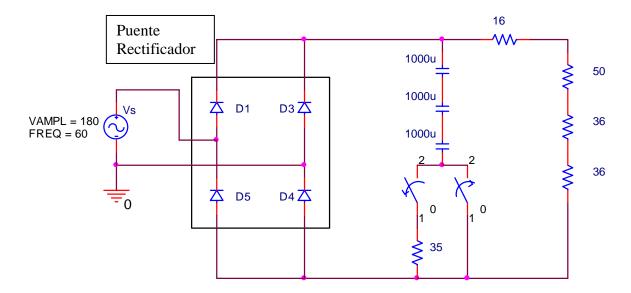

#### 4.1.- CARGA NO LINEAL.

Como una carga no lineal convencional se propuso usar un rectificador no controlado a base de diodos, esto es, un convertidor AC-DC clásico. La carga es monofásica, como ya se había mencionado, con un voltaje de línea de 127Vrms y la corriente que consume es de aproximadamente 10A de pico, estos valores se usaron para especificar los parámetros de los MOSFETs. Se buscó además que la mayoría de los componentes excedieran al menos en un 25% las exigencias en voltaje, corriente y potencia para evitar sobrecalentamientos y posibles fallas en su funcionamiento. El diseño esquemático de la carga no lineal es el que se muestra en la Fig. 4.1.

Fig. 4.1.- Carga no lineal.

#### Características de la carga no lineal:

- Potencia 1.5 KW.

- Voltaje en el lado de continua: 154 V de pico aprox.

- Resistencia de limitación para la corriente de 35 Ohms @ 35 W al 10%. Utilizada solo en el momento de conexión de la carga para evitar picos de corriente muy altos, momentos después se desconectaba.

- Capacitancia total 333.33 uF: 3 capacitores en serie de 1000 uF a 450VDC

- Resistencia total 138 Ohms: 16 Ohms @ 200W al 10%, 50 Ohms @ 160W al 5% y 2 de 36 Ohms @ 400W al 10% conectadas en serie.

Interruptores manuales para conexión a línea con capacidad de 25 A.

- Puente rectificador de 20 A, GBPC3504

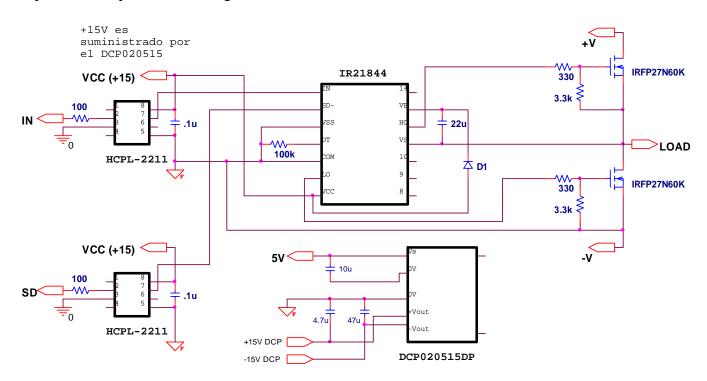

#### 4.2.- ETAPA DE POTENCIA.

Como ya se mencionó anteriormente, dada la relativa baja potencia del prototipo se utilizaron dispositivos MOSFETs. Se escogieron dispositivos IRFP27N60K con especificaciones 600V, 27 A. Como se estableció previamente en el capítulo II, el trabajo de los dos MOSFETs utilizados en la rama debe de ser complementario y se debe de establecer un tiempo muerto entre el encendido de uno y el apagado del otro para evitar cortocircuitos. Para esto se escogió el impulsor comercial IR21844 normalmente usado en arreglos de medio puente; en este dispositivo se tiene la capacidad de programar el tiempo muerto para el encendido de los MOSFETs, y posee una entrada de desactivación (SD o SHUTDOWN) que permite controlar la desactivación inmediata del VSI, en este caso formado solo por una rama de MOSFETs. Para aislar galvánicamente las señales de entrada al impulsor se utilizaron optoacopladores HCPL-2211.

Debido de la topología propuesta, cabe destacar que no se cuenta con una referencia a tierra para el medio puente de MOSFETS, lo cual obliga a colocar fuentes de alimentación "flotantes" en el lado de potencia para tener un correcto funcionamiento del impulsor. De hecho, el punto de referencia se establece en el voltaje negativo del capacitor inferior del filtro, normalmente llamado COM. Para este propósito se utilizó el convertidor DC/DC no regulado con aislamiento galvánico modelo DCP020515DP. El diseño esquemático se presenta en la Fig. 4.2.

Fig. 4.2.- Etapa de potencia donde se muestra el impulsor de los MOSFETs.

Componentes usados en el resto de la etapa de potencia:

- Dos capacitores de 6800 μF a 525 VDC.

- Inductor de 6 mH a 16 A.

- Dos contactores de estado sólido de un-polo-un-tiro c/u, a 30 A, para montaje de panel, con voltaje de bobina de 12 VDC.

- Interruptor termomagnético a la entrada de alimentación general con capacidad de 25A.

- Fusible rápido de 12 A en el punto de interconexión del inductor con la línea de alimentación.

- Resistencia de 50 Ohms @ 160W al 5% para carga de capacitores. Se conectaba en serie con el inductor al momento de conexión del filtro a la línea de alimentación para evitar picos de corriente muy altos. Una vez cargados los capacitores se cortocircuitaba para eliminar su efecto en el sistema.

#### 4.3.- TARJETAS DE SENSADO.

Todas estas tarjetas han sido diseñadas para entregar una señal de voltaje en el rango de [-10,10] V, ya que es este rango el que permite la tarjeta de control dSPACE. Más aún, todas ellas se diseñaron para garantizar aislamiento galvánico, debido a lo elevado de las tensiones en la etapa de potencia, y fueron elaboradas en forma modular, esto es, cada una en un circuito impreso por separado, lo cual permite un fácil mantenimiento en caso de sufrir algún daño o desperfecto.

#### A. Sensor de corriente

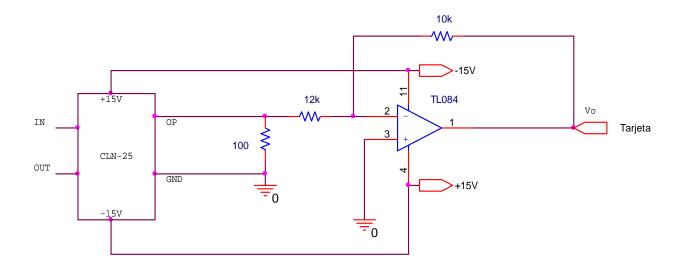

Para la adquisición de la corriente de línea se utilizó el sensor de efecto Hall de lazo cerrado CLN-25, con capacidad de medición de corriente tanto en alterna como en directa. Se configuró de tal manera que tuviera la capacidad de sensar hasta 25 A Se utilizó un amplificador operacional para ajustar el nivel de voltaje de la señal de medición. El diseño esquemático se muestra en la Fig. 4.3.

Fig. 4.3.- Adquisición de corriente de línea.

#### B. Sensor de voltaje de línea

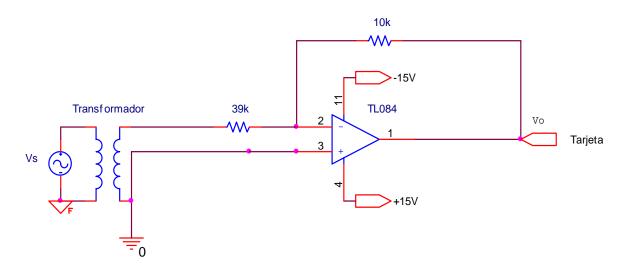

Para sensar el voltaje de la línea de alimentación se optó por utilizar un transformador, cuya salida de voltaje se ajusta a través de un amplificador operacional. La Fig. 4.4 muestra el diseño esquemático para la adquisición del voltaje de línea.

Fig. 4.4.- Adquisición del voltaje de línea.

#### C. Sensores de tensión de los capacitores

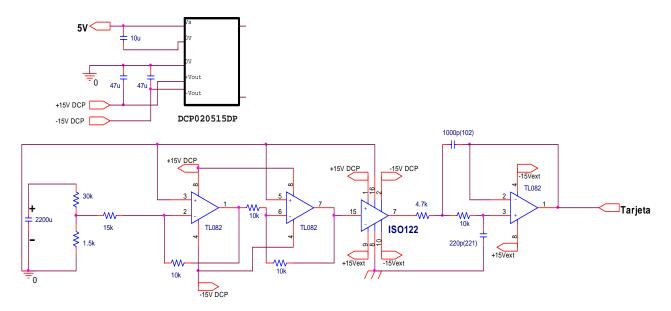

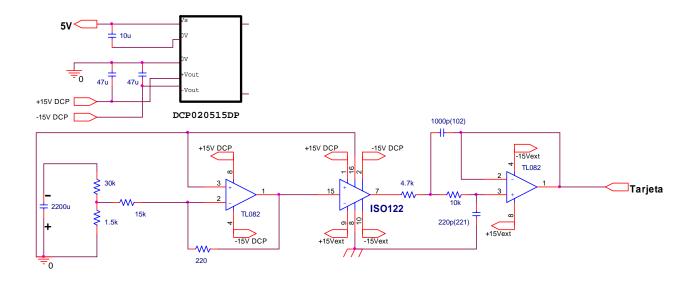

La adquisición de los voltajes de los capacitores implicó un diseño un poco más complicado, ya que además de ajustar el nivel de voltaje para su adquisición era necesario tener un aislamiento galvánico entre la etapa de potencia y la tarjeta de control. Para estos fines se utilizó el amplificador de aislamiento ISO122, el cual requería a su vez una fuente de alimentación aislada, para lo cual se utilizó nuevamente el DCP020515DP. Desafortunadamente el uso de cualquier dispositivo de conmutación, como lo es el ISO122, introduce distorsión en la señal de medición, por lo que se hace necesario colocar un filtro pasa bajas (LPF) en la misma etapa de acondicionamiento antes de ser enviado a la tarjeta de control. Cabe mencionar que este filtro esta diseñado para no afectar de manera considerable la respuesta en frecuencia de nuestro circuito. Este filtro fue diseñado con amplificadores operacionales, con frecuencia de corte a 50 KHz. Dado que se trata del sensado de dos voltajes, uno positivo y uno negativo, fue conveniente diseñar dos circuitos diferentes. El diseño esquemático de los circuitos de adquisición del voltaje de los capacitores, positivo y negativo, se muestran en las Fig. 4.5. y 4.6, respectivamente.

Fig. 4.5.- Adquisición del voltaje positivo del capacitor.

Fig. 4.6.- Adquisición del voltaje negativo del capacitor.

#### 4.4.- TARJETA DE CONTROL.

Para implementar el controlador propuesto se utilizó la tarjeta dSPACE DS1103 PPC. Esto nos permitió trabajar en un ambiente gráfico, cuya programación se facilitó considerablemente gracias a los programas de simulación hechos en MATLAB. Un punto importante de mencionar en esta etapa de implementación es que los filtros resonantes no fueron implementados directamente, sino que se usaron filtros pasa-bandas con un ancho de banda muy angosto, para reproducir el funcionamiento de los filtros resonantes. Esto se realizó con el objetivo de ganar tiempo en el proceso de la tarjeta de control, además de implementar los filtros de una manera más simple. La tarjeta incluye puertos de entrada y salida (I/O) digitales, convertidores análogicos-digitales (ADC) y digital-analógicos (DAC), así como canales para los generadores de pulsos (PWM). En el Apéndice B, se muestra un diagrama de los puertos disponibles y se remarcan los puertos utilizados.

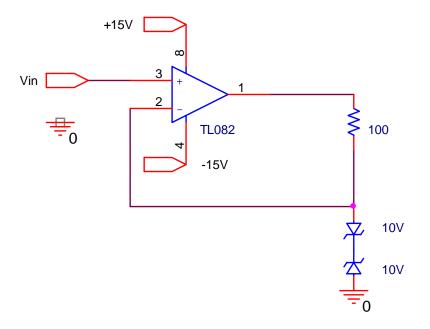

#### A. Tarjeta de interfaz de entrada

Dado que la entrada a los puertos DACs está limitada a  $\pm 10$  V, según especificaciones de la dSPACE, se diseño una tarjeta de interfaz para proteger a la tarjeta de control. El diseño esquemático se muestra en la Fig. 4.7. Esta tarjeta de interfaz limita el voltaje de entrada, evitando así que una posible falla en las tarjetas de sensado dañe a la tarjeta de control.

Fig. 4.7.- Limitador de voltaje.

#### B. Tarjeta de Interfaz de Salida

Para proteger las señales de salida y de PWM de la dSPACE, se diseñó otra tarjeta de interfaz que consiste en reforzadores (BUFFER) de señales, la cual impide que alguno de los puertos de salida de la tarjeta de control se pudiera dañar por una exigencia de corriente que sobrepasara las especificaciones de la tarjeta.

#### C. Maniobras de Operación

Para poder arrancar el prototipo de pruebas a controlarse con la ley de control propuesta es necesario seguir el siguiente procedimiento de encendido (ver Fig. 4.8):

Fig. 4.8.- Esquemático del prototipo para maniobras de operación

- 1.- Energizado del sistema: Implica conectar a la línea de alimentación el sistema vía el interruptor termomagnético TM1 para encender las fuentes de alimentación para los diversos sensores y tarjetas de interfaz. En este paso los contactos SW2 para la carga y SW3 para la conexión del prototipo a la línea de alimentación permanecen abiertos.

- 2.- Carga de capacitores: Es necesario llevar las condiciones iniciales de voltaje de capacitores a un determinado valor inicial para garantizar que en el arranque de nuestra ley de control no se produzca un pico de corriente muy elevado al tratar de llevar los capacitores a su nivel de referencia. La carga de los capacitores se hace a través de los diodos en antiparalelo que vienen incluidos en los MOSFETs, y la corriente se limita con una resistencia de protección Rp en serie con el inductor L que se conecta a la línea de alimentación vía el interruptor SW3; después de haber sido cargados los capacitores, ésta resistencia se cortocircuita vía el interruptor SW4 para que no afecte en el funcionamiento del sistema. En este punto los interruptores SW2, SW3 de la carga no lineal y de conexión del prototipo están cerrados, sin embargo, los MOSFETs no están activados aun gracias a la entrada de desactivación del impulsor (SD o SHUTDOWN).

- 3.- Arranque de la ley de control propuesta: Este paso se ejecuta con la tarjeta de control. Esta envía una señal que activa al VSI (SD=0) al mismo tiempo que se envía la señal de PWM al impulsor. Al inicio todos los filtros resonantes están desactivados. Dado que la carga no lineal esta desconectada, la ley de control forza al sistema a comportarse como un rectificador síncrono, esto es, se lleva a cabo la regulación y balance de los capacitores, con una señal de corriente de línea muy cercana a la forma del voltaje de la fuente, esto es, con un PF cercano a la unidad.

- 4.- Energizado de la carga no lineal: La carga se conecta a la red usando el interruptor SW2. Para evitar un pico de corriente muy alto, se coloca en cascada con los capacitores la resistencia de 35 Ohms como se muestra en la Fig. 4.1, esta resistencia es posteriormente cortocircuitada para obtener la carga completa. La conexión de la carga se realiza como paso final una vez habilitada la ley de control. En este momento, los capacitores estando ya regulados y balanceados, sufren un pequeño transitorio, mientras la corriente trata de seguir a la deseada.

- 5.- Habilitación de los filtros resonantes: Una vez pasado el transitorio de los voltajes de los capacitores por la conexión de la carga no lineal, se procede a conectar uno a uno los filtros resonantes del lazo interno de control. Esto evita que surja un sobretiro muy grande en la corriente de referencia que obligaría a crecer a la corriente de línea, lo cual a su vez abriría las protecciones.

- 6. Apagado del prototipo: Cuando el prototipo de pruebas está conectado no resulta conveniente desenergizar de inmediato para apagar el sistema, ya que esto puede llevar a que se dañen ciertos componentes como lo son el inductor y los MOSFETs. Para apagar el sistema es necesario primero desactivar el VSI, desconectar la carga no lineal, desconectar el inductor de la línea y finalmente desernegizar el sistema completo, esto es descargar los capacitores. La descarga de los capacitores se hace a través de las resistencias de pérdidas y se tardan alrededor de 20 segundos en estar descargados por completo.

#### D. Protecciones

Gracias a la entrada de desactivación (SD o SHUTDOWN) que ofrece el impulsor IR21844, es posible tener control de la desactivación del VSI, lo cual permite programar en la tarjeta de control las protecciones necesarias para garantizar que el sistema se mantendrá en buen estado en caso de presentarse condiciones anormales de operación. Básicamente, esto permite deshabilitar al VSI en el momento en que se alcanza alguna condición de operación anormal. Las protecciones que se establecieron en la tarjeta incluyen:

- Condiciones iniciales en los voltajes de los capacitores por encima de un cierto valor, en este caso arriba de 100VDC.

- Protección para evitar un desbalance excesivo en los capacitores

- Elevación de los voltajes de los capacitores más allá de cierto margen

- Desactivación cuando la corriente de carga aumente o disminuya más allá de cierto margen.

Fig. 4.9.- Fotografía carga no lineal.

Fig. 4.10.- Fotografía impulsor de los MOSFETs.

Fig. 4.11.- Fotografía filtro activo paralelo monofásico.

Fig. 4.12.- Fotografía filtro activo paralelo monofásico y carga no lineal.

## CAPÍTULO V

## **RESULTADOS EXPERIMENTALES**

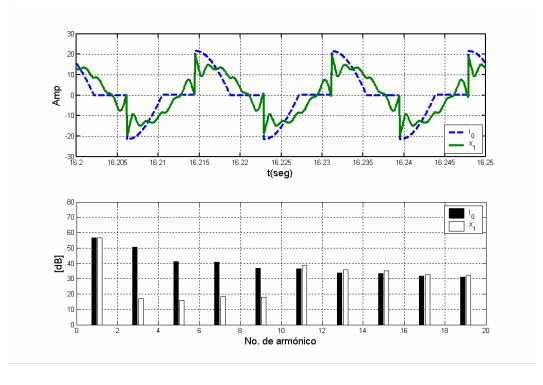

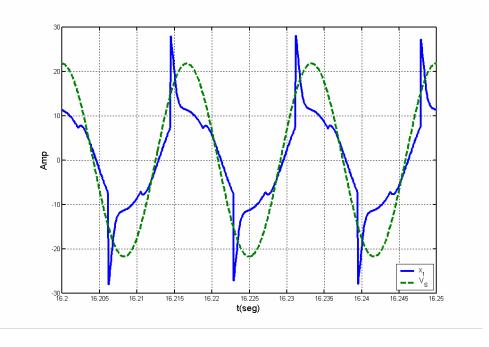

En este capítulo se presentan los resultados de las pruebas realizadas en el prototipo. Estas pruebas muestran las respuestas en tiempo cuando se habilitan uno a uno los filtros resonantes en la ley de control propuesta. Hemos implementado también la ley de control convencional para mostrar las mejoras en desempeño que se obtienen siguiendo la ley de control propuesta.

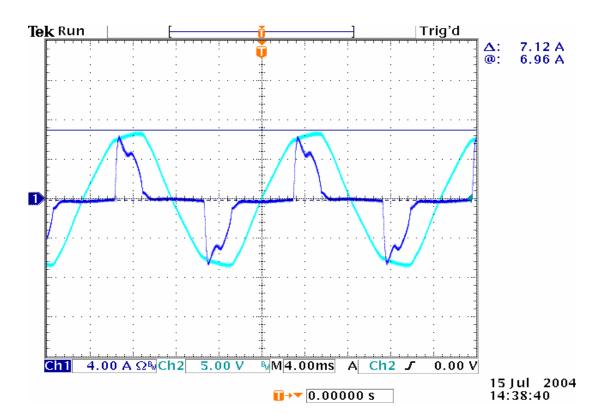

Las graficas de la corriente de carga debida al puente rectificador no controlado y el voltaje de la línea de alimentación se reportan en la Fig. 5.1.

Fig. 5.1.- Señales de voltaje de línea (CLARO) y corriente de carga (OSCURO)

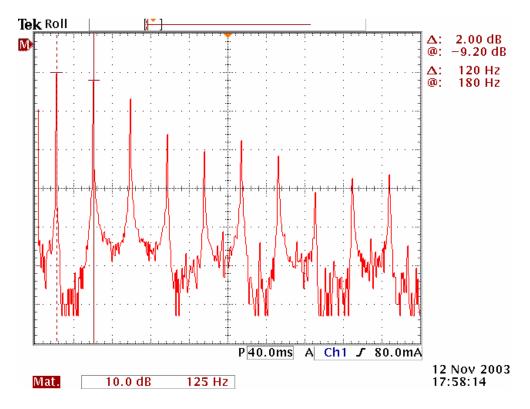

Fig. 5.2.- Contenido armónico de la señal de corriente de carga

En esta gráfica se puede apreciar que la corriente de carga tiene una forma de onda periódica distorsionada conteniendo fundamentalmente los armónicos impares (Fig. 5.2), tal y como se usó en las simulaciones. Nótese también que el voltaje de línea tiene una visible distorsión con respecto a una señal senoidal pura, lo cual sin embargo no afecta el funcionamiento básico de nuestro controlador, dado que esta perturbación también fue considerada en el diseño del mismo.

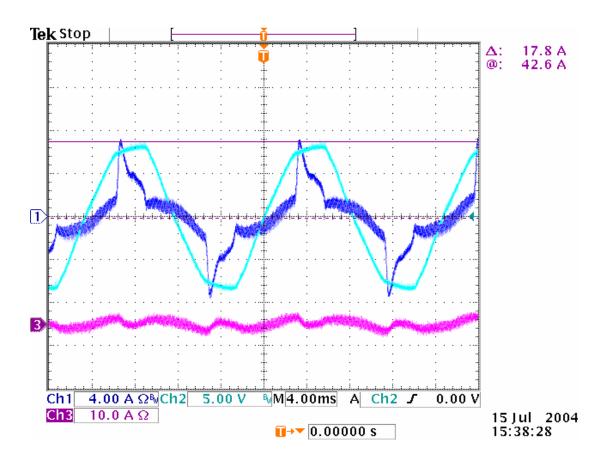

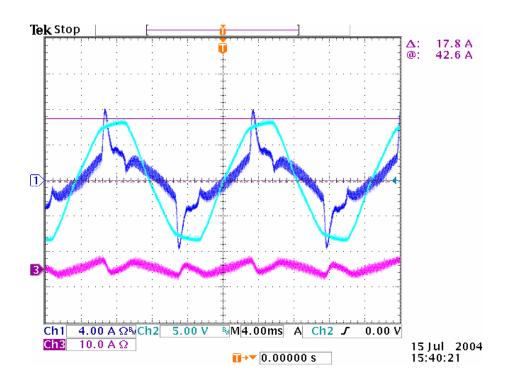

A fin de resaltar las mejoras en desempeño del controlador propuesto, implementamos el controlador convencional. Este último incluye un control proporcional-integral (PI) como lazo interno de corriente. Hemos, sin embargo, mantenido el lazo de control externo para el balance de los capacitores similar al propuesto, ya que la ley convencional se basa únicamente en el balance vía las resistencias de ecualización, como se explico en el Capítulo II. Los resultados usando la ley convencional se reportan en la Fig. 5.3, en donde se muestra también la corriente inyectada a la línea por el filtro activo.

Fig. 5.3.- Señal de corriente de línea con el control convencional (**ARRIBA-OSCURO**), señal de voltaje de línea (**ARRIBA-CLARO**) y señal de corriente inyectada por el filtro activo (**ABAJO**).

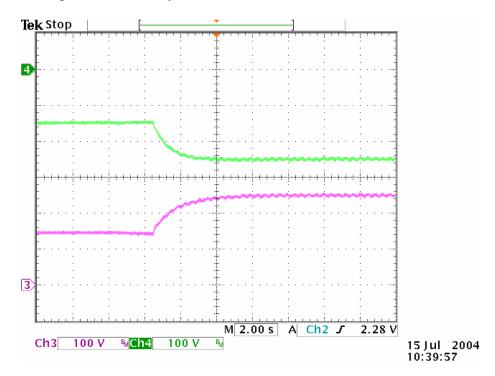

Se puede apreciar que el controlador PI no logra llevar a la corriente de línea a estar en fase con el voltaje de fuente, y más aún, la corriente resultante mantiene casi la misma distorsión armónica que la corriente de la carga, lo que coincide con los resultados obtenidos en la simulación para el controlador convencional que aparecen en el Capítulo III. En la Fig. 5.4 se reportan los resultados obtenidos para la regulación y desbalance del voltaje de los capacitores en la ley convencional.

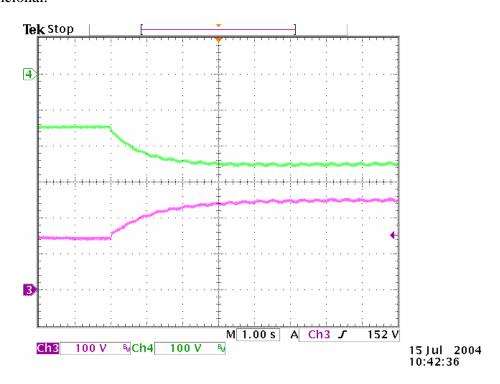

Fig. 5.4.- Señal de voltaje del capacitor superior (**ARRIBA**) y señal de voltaje del capacitor inferior (**ABAJO**).

En la implementación del controlador propuesto usando la dSPACE, se tiene la capacidad de añadir en línea, uno a uno, los filtros resonantes para compensar los armónicos en consideración, así como de variar la ganancia asociada a cada filtro resonante. Lo anterior resulta muy conveniente, ya que permitió inyectar la compensación de cada armónico uno a uno sin necesidad de desconectar y volver a programar o cambiar ganancias fuera de línea.

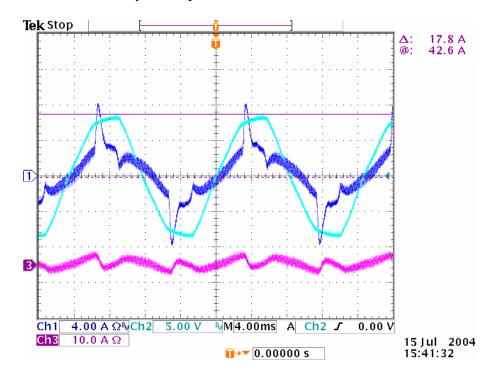

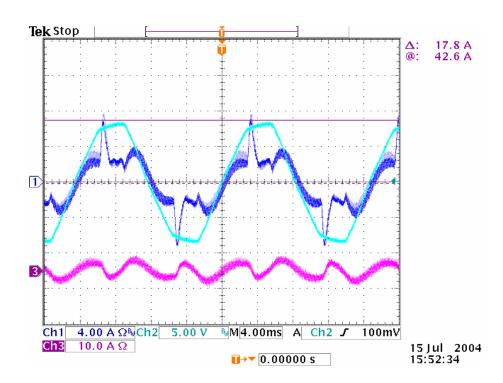

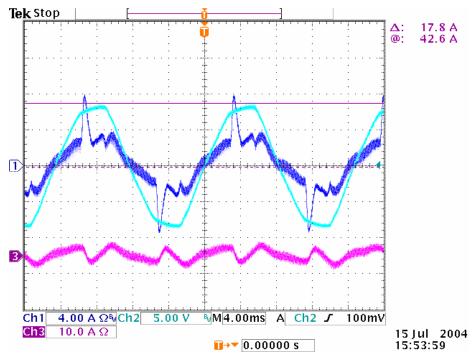

Los resultados para el controlador propuesto con la compensación de los armónicos incluyendo uno a uno se muestran en las Fig. 5.5 a 5.8. En la Fig. 5.4 se muestra la respuesta incluyendo únicamente los filtros resonantes para los armónicos 1 y 3, en las siguientes figuras se añaden progresivamente, uno por uno, los filtros de orden superior hasta llegar a la Fig. 5.7 que incluye la compensación de los armónicos 1, 3, 5, 7 y 9.

Fig. 5.5.- Señal de corriente de línea con compensación para los armónicos 1 y 3 (ARRIBA-OSCURO), señal de voltaje de línea (ARRIBA-CLARO) y señal de corriente inyectada por el filtro activo (ABAJO).

Fig. 5.6.- Señal de corriente de línea con compensación para los armónicos 1, 3 y 5 (ARRIBA-OSCURO), señal de voltaje de línea (ARRIBA-CLARO) y señal de corriente inyectada por el filtro activo (ABAJO).

Fig. 5.7.- Señal de corriente de línea con compensación para los armónicos 1, 3, 5 y 7 (ARRIBA-OBSCURO), señal de voltaje de línea (ARRIBA-CLARO) y señal de corriente inyectada por el filtro activo (ABAJO).

Fig. 5.8.- Señal de corriente de línea con compensación para los armónicos 1, 3, 5, 7 y 9 (**OBSCURO**), señal de voltaje de línea (**CLARO**) y señal de corriente inyectada por el filtro activo (**INFERIOR**)

Se observa de las figuras anteriores que tan solo incluyendo los armónicos 1 y 3 se logran excelentes resultados comparados con aquellos debidos a la ley convencional. Se puede notar que con la ley propuesta se logra poner en fase a la corriente de línea con el voltaje de alimentación, más aún, a medida que se añaden los filtros resonantes, se logra una corriente de línea más cercana a la forma del voltaje de alimentación como se esperaba, con lo que se logra un factor de potencia cada vez más cercano a la unidad. Se observa también un ligero aumento y una mejor definición en la corriente inyectada por el filtro activo a medida que se incluyen los filtros resonantes.

Los resultados para la regulación del voltaje de los capacitores y el desbalance de los mismos usando la ley propuesta se reportan en la Fig. 5.8. En esta figura se muestra el transitorio de los voltajes al arrancar la ley de control, se observa que ambos capacitores alcanzan el mismo nivel después de un transitorio relativamente pequeño. Estos resultados se pueden considerar prácticamente iguales a los resultados obtenidos con el controlador convencional.

Fig. 5.9.- Señal de voltaje del capacitor superior (**ABAJO**) y señal de voltaje del capacitor inferior (**ARRIBA**).

Las gráficas anteriores nos permiten demostrar que la ley de control propuesta cumple muy cercanamente con los objetivos establecidos. Esto es, seguimiento de corriente, regulación y balance de voltajes. Se observa que la corriente aun contiene cierta distorsión, lo cual podría ser solucionado incluyendo más filtros resonantes a armónicos de orden superior.

## CAPÍTULO VI

### **CONCLUSIONES Y TRABAJO A FUTURO**

En este trabajo de tesis se presenta una topología de filtro activo para la cual se hizo un análisis completo de su funcionamiento, se obtuvo el modelo matemático y se propuso una ley de control. La topología propuesta presenta la ventaja de utilizar una sola rama de interruptores, sin embargo, los dispositivos semiconductores usados como interruptores deben de ser de alta capacidad, ya que se maneja directamente toda la potencia a través de ellos. De esto podemos concluir que la ventaja se presenta sólo en la cantidad de dispositivos semiconductores, y no en disminución de potencia manejada por cada uno de ellos, como podría ser en el caso de un convertidor multinivel.

La aparición de dos capacitores en el lado de corriente continua presenta el problema del balance de los voltajes de los mismos. Para resolver este problema fue necesario introducir un grado de libertad extra en la referencia de corriente, ya que de otra manera, no era posible garantizar un balance correcto de los voltajes. Se observó que las resistencias de ecualización (o de pérdidas) que se colocan en paralelo con los capacitores proveen de una mayor estabilidad al sistema, ya que introducen un término de amortiguamiento, pero su uso, aunque ayuda a resolver el problema del desbalance de voltajes en los capacitores, hace ineficiente al sistema. El grado de libertad que se agrega en la referencia de corriente permite simular el funcionamiento de las resistencias ecualizadotas, con la capacidad de acelerar la convergencia a cero de la diferencia de los voltajes de los capacitores, permitiendo así garantizar el balance de los mismos. Un punto importante a mencionar es que la distorsión, que este grado de libertad introduce en la referencia de corriente, desaparece en el estado estacionario.

Una contribución importante de este trabajo es la reducción de las leyes adaptables a simples filtros resonantes, lo cual confirma el principio de modelo interno, así el banco de filtros resonantes representa el modelo de la perturbación a compensar, en este caso una perturbación periódica formada por componentes armónicos. Más aún, cabe mencionar que nuestro método es selectivo, ya que solo compensará a un grupo de armónicos

seleccionados. Es necesario mencionar que los filtros resonantes fueron implementados en la tarjeta de control como filtros pasa-banda de banda muy angosta, lo cual ciertamente introduce errores al momento de compensar el armónico seleccionado. A estos errores podemos atribuir el incremento, aunque acotado, de los armónicos de orden superior que no se compensan; sin embargo, el uso de filtros pasa-bandas provee de cierta robustez a nuestro sistema ante cambios en la frecuencia de la línea de alimentación, la cual fue supuesta constante.

Los resultados de simulación y experimentales muestran que la ley de control propuesta cumple en su mayor parte con las exigencias de los objetivos establecidos, pero a su vez muestran que es necesario incluir un mayor número de filtros resonantes para la compensación de armónicos de orden superior. Se observó también la aparición de un ligero ruido a muy alta frecuencia causado por las conmutaciones de los dispositivos semiconductores de potencia.

Para finalizar, como trabajo a futuro se plantean las siguientes actividades:

- 1. Mejorar las tarjetas de sensado, interfaz y control de los interruptores para optimizar el prototipo de pruebas presentado.

- 2. Implementar la ley de control en una tarjeta de la familia DSP24X. Esto permitirá tener el control del prototipo de pruebas con un dispositivo más compacto, dinámico y económico.

- 3. Probar otro tipo de leyes de control como las basadas en control repetitivo recientemente propuestas en [18].

- 4. Diseñar un prototipo para potencias mayores.

- 5. Tratar el caso trifásico.

## **APÉNDICE A**

# PUERTOS USADOS DE LA TARJETA dSPACE DS1103

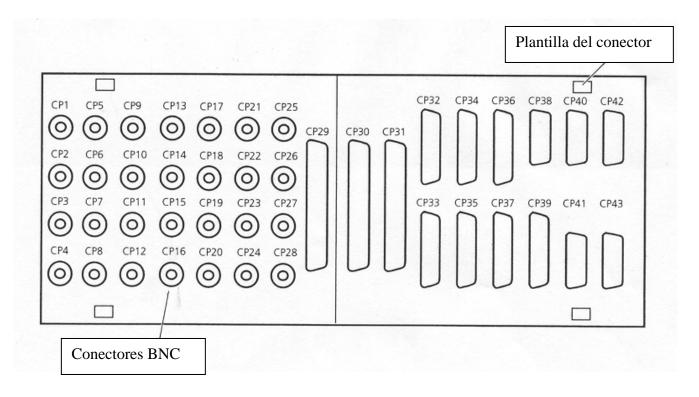

Los paneles de conectores CP1103 y CPL1103 proporcionan conexiones fáciles de usar entre la DS1103 y los dispositivos que se conectarán a esta. Los dispositivos pueden ser individualmente conectados, desconectados o intercambiados sin la necesidad de ser soldados. Esta característica simplifica la construcción del sistema, hacer pruebas y arreglar desperfectos.

A continuación se muestra la tabla de los conectores BNC hembra, en donde la coraza está conectada a GND (CP1...CP28).

| Connector | Signal | Connector | Signal |

|-----------|--------|-----------|--------|

| CP1       | ADCH1  | CP15      | ADCH15 |

| CP2       | ADCH2  | CP16      | ADCH16 |

| CP3       | ADCH3  | CP17      | ADCH17 |

| CP4       | ADCH4  | CP18      | ADCH18 |

| CP5       | ADCH5  | CP19      | ADCH19 |

| CP6       | ADCH6  | CP20      | ADCH20 |

| CP7       | ADCH7  | CP21      | DACH21 |

| CP8       | ADCH8  | CP22      | DACH22 |

| CP9       | ADCH9  | CP23      | DACH23 |

| CP10      | ADCH10 | CP24      | DACH24 |

| CP11      | ADCH11 | CP25      | DACH25 |

| CP12      | ADCH12 | CP26      | DACH26 |

| CP13      | ADCH13 | CP27      | DACH27 |

| CP14      | ADCH14 | CP28      | DACH28 |

Se muestra ahora el conector para entradas y salidas digitales (Digital I/O Connector CP30), en donde se utilizaron las terminales 17(GND) y 1(IO0).

| Digital I/O<br>Connector (CP30) | Pin | Signal | Pin | Signal | Pin | Signal     |

|---------------------------------|-----|--------|-----|--------|-----|------------|

| 33                              | 17  | GND    |     |        | 50  | VCC (+5 V) |

|                                 | 16  | 1030   | 33  | IO31   | 49  | /INT3      |

| 17 50                           | 15  | 1028   | 32  | 1029   | 48  | /INT2      |

|                                 | 14  | 1026   | 31  | 1027   | 47  | /INT1      |

|                                 | 13  | 1024   | 30  | 1025   | 46  | /INTO      |

|                                 | 12  | 1022   | 29  | 1023   | 45  | GND *      |

|                                 | 11  | 1020   | 28  | IO21   | 44  | GND        |

|                                 | 10  | IO18   | 27  | 1019   | 43  | GND        |

|                                 | 9   | 1016   | 26  | 1017   | 42  | GND        |

|                                 | 8   | 1014   | 25  | 1015   | 41  | GND        |

|                                 | 7   | 1012   | 24  | 1013   | 40  | GND        |

|                                 | .6  | IO10   | .23 | 1011   | 39  | GND        |

| 1 34                            | 5   | 108    | 22. | 109    | 38  | GND        |

| 1 34                            | 4   | 106    | 21  | 107    | 37  | GND        |

| <br>18                          | 3   | 104    | 20  | 105    | 36  | GND        |

|                                 | 2   | 102    | 19  | 103    | 35  | GND        |

|                                 | 1   | 100    | 18  | 101    | 34  | GND        |

También se utilizó el conector esclavo de entradas/salidas (Slave I/O Connector CP31), las terminales que se utilizaron fueron 1(GND) y 7(SPWM1).

| Slave   |          | (CP31) | Pin     | Signal     | Pin     | Signal |

|---------|----------|--------|---------|------------|---------|--------|

| 1-10    |          | 1      | GND     |            |         |        |

|         | 00000000 | 20     | 2       | SCAP1      | 20      | GND    |

|         |          |        | 3       | SCAP3      | 21      | SCAP2  |

|         |          |        | 4       | GND        | 22      | SCAP4  |

|         |          |        | 5       | ST2PWM     | 23      | ST1PWM |

|         |          |        | 6.      | GND        | 24 .    | ŞT3PWM |

| 0 0 0 0 |          | 7      | SPWM1   | 25         | GND     |        |

|         |          | 8      | SPWM3   | 26         | SPWM2   |        |

|         |          | 9      | SPWM5   | 27         | SPWM4   |        |

|         | 0 0 0    |        | 10      | SPWM7      | 28      | SPWM6  |

|         |          |        | 11      | SPWM9      | 29      | SPWM8  |

| 19 00   | 37       | 12     | STMRCLK | 30         | GND     |        |

|         |          | 13     | GND     | 31         | STMRDIR |        |

|         |          | 14     | STINT1  | 32         | SPDPINT |        |

|         |          | 15     | GND     | 33         | STINT2  |        |

|         |          | 16     | SSIMO   | 34         | SSOMI   |        |

|         |          |        | 17      | SCLK       | 35      | SSTE   |

|         |          |        | 18      | SXF        | 36      | SBIO   |