# INSTITUTO POTOSINO DE INVESTIGACIÓN CIENTÍFICA Y TECNOLÓGICA, A.C.

# **POSGRADO EN CIENCIAS APLICADAS**

# Controller for compensation of unbalance and harmonic distortion in an UPS inverter

Tesis que presenta

Andrés Alejando Valdez Fernández

Para obtener el grado de

# Maestro en Ciencias Aplicadas

En la opción de

**Control y Sistemas Dinámicos**

Director de la Tesis: Dr. Gerardo Escobar Valderrama

San Luis Potosí, S.L.P., Agosto de 2005.

Instituto Potosino de Investigación Científica y Tecnológica, A.C.

## Acta de Examen de Grado

#### COPIA CERTIFICADA

El Secretario Académico del Instituto Potosino de Investigación Científica y Tecnológica, A.C., certifica que en el Acta 007 del Libro Primero de Actas de Exámenes de Grado del Programa de Maestría en Ciencias Aplicadas en la opción de Control y Sistemas Dinámicos está asentado lo siguiente:

En la ciudad de San Luis Potosí a los 5 días del mes de agosto del año 2005, se reunió a las 11:00 horas en las instalaciones del Instituto Potosino de Investigación Científica y Tecnológica, A.C., el Jurado integrado por:

| Dr. Jesús Leyva Ramos             | Presidente      | IPICYT |

|-----------------------------------|-----------------|--------|

| Dr. Gerardo Escobar Valderrama    | Secretario      | IPICYT |

| Dr. Jorge Alberto Morales Saldaña | Sinodal externo | UASLP  |

a fin de efectuar el examen, que para obtener el Grado de:

MAESTRO EN CIENCIAS APLICADAS EN LA OPCIÓN DE CONTROL Y SISTEMAS DINÁMICOS

sustentó el C.

#### Andrés Alejandro Valdez Fernández

sobre la Tesis intitulada:

Controller for compensation of unbalance and harmonic distortion in an UPS inverter

que se desarrolló bajo la dirección de

Dr. Gerardo Escobar Valderrama

El Jurado, después de deliberar, determinó

#### **APROBARLO**

Dándose por terminado el acto a las 13:00 horas, procediendo a la firma del Acta los integrantes del Jurado. Dando fé el Secretario Académico del Instituto.

A petición del interesado y para los fines que al mismo convengan, se extiende el presente documento en la ciudad de San Luis Potosí, S.L.P., México, a los 5 días del mes agosto de 2005.

División de Matemáticas Aplicadas y Sistemas Computacionales

Maestría en Ciencias Aplicadas con opción en Control y Sistemas Dinámicos

CONTROLLER FOR COMPENSATION OF UNBALANCE AND HARMONIC DISTORTION IN AN UPS INVERTER

Ing. Andrés Alejandro Valdez Fernández

Sinodales:

Dr. Gerardo Escobar Valderrama (Director de Tesis)

Dr. Jesús Leyva Ramos (Sinodal interno)

Dr. Jorge Alberto Morales Saldaña (Sinodal externo)

San Luis Potosí, S.L.P, México, Agosto de 2005

to my parents and my sisters with gratefulness...

### ACKNOWLEDGMENTS

First, I would like to thank to my advisor Dr. Gerardo Escobar for his valuable advising, support, friendship and trust during the development of my research work. I also would to like to express my gratitude to Dr. Jesús Leyva, Dr. Jorge Morales, Dr. Haret Rosu and Dr. Daniel Melchor for his valuable comments and useful suggestions to this document.

It is a pleasure to thank to Dr. Arturo Zavala, Dr. Daniel Melchor, Dr. David Lizrraga, Dr. Elisabeth Huber, Dr. Haret Rosu, Dr. Hugo Cabrera and Dr. Jess Leyva, who imparted rewarding M.Sc. courses, which are a fundamental part in my formation.

Quiero agradecer a mi papá por su inagotable e incondicional apoyo aún sin estar ya en este mundo de expiación. Quiero agradecer también a mi mamá y mis hermanas Socorrito, Chuy y Arlene quienes me han apoyado en cada proyecto de mi vida. Debo agradecer también a Bere ya que aunque no es muy expresiva, siempre me ha apoyado, especialmente en los momentos difíciles.

I want to thank to the power electronics crew Panfilo, Misael, Michael and Raymundo for their support and friendship in the laboratory.

I also want to acknowledge to my generation companions Gris (gray), Sosa (niño sosa) Rafael (rafa), Gabriel (gabriel), Eduardo (lalo), Leonardo (leo), Armando (el matón), Felipe (mike), Angélica, José Manuel (nanomorro), Eduardo (cruzote), Jaime (jaime), Pedro (may), Maria (pili), Jorge (george), José (napoles), Pedro (Palomares) y Marcia (Vianey) for their friendship and the hundreds of beers shared. I would like to acknowledge whom show me that work can be done in an environment of friendship and enthusiasm and for all those dominos matches with my hackios and not hackios friends Arturo, Bere, Carlos, Enrique, Gabriel, Gray, Israel, Luis (ardilla), Memo, and Pablo. I should not forget to express gratitude to Arturo de la Vega for his accurate correction with the English in the first version of this manuscript. I also want to thank Victor for his support in the library.

Finaly, I thank to COCACyT for the financial support during this thesis work.

My gratitude for all.

Andrés Alejandro Valdez Fernández San Luis Potosí, México August 2005

### RESUMEN

En este trabajo se propone un controlador basado en técnicas de control adaptable para una fuente ininterrumpida de voltaje (UPS). El controlador propuesto está basado en la medida de una corriente combinada usando un mismo sensor tipo dona para tal efecto. Esta última se forma a partir de una combinación lineal de las corrientes de capacitor y carga. El propósito de utilizar esta corriente combinada es, por una parte, obtener un comportamiento muy similar al obtenido con un controlador basado en la corriente de capacitor y por otra parte, poder obtener fácilmente un estimado de la corriente de inductor para propósitos de seguridad.

El controlador propuesto es capaz de compensar el desbalance y distorsión armónica en la carga a pesar de que esta sea de naturaleza no lineal. Técnicas de control adaptable son utilizadas para compensar las perturbaciones en los parámetros del sistema. Gracias a una sencilla transformación, el controlador propuesto tiene una forma muy similar a la de un controlador convencional, solo que este incluye un banco de filtros resonantes, los cuales confirman el Principio del Modelo Interno. El controlador propuesto está basado en descripciones en el dominio de la frecuencia de perturbaciones periódicas, es decir, incluye ambas componentes simétricas, llamadas secuencias positiva y negativa, de esta manera se puede trabajar bajo condiciones de desbalance. Como consecuencia, el controlador propuesto compensa un grupo seleccionado de componentes armónicos. En este trabajo se propone además, un estimador muy sencillo obtenido en términos de la corriente combinada y de la corriente desconocida de capacitor, debido a que la corriente combinada contiene informacion de la corriente de carga, el estimador propuesto responde de manera inmediata en caso de que una condición de sobre corriente se presente en la carga.

#### Resumen

Por otra parte, en este trabajo de tesis, se explica con detalle la construcción de un prototipo UPS trifásico de tres hilos que soporta una potencia de 1.5 KVA, el cual fue construido para probar de manera práctica el controlador y el estimador propuestos. En este prototipo se consideran todas las precauciones necesarias, tales como, corto circuito, bajo voltaje, sobre voltaje, aislamiento galvánico entre la etapa de potencia y la etapa de control, etc. En esta implementacion tanto el controlador como el estimador propuestos son implementados por medio de una tarjeta de control dSPACE modelo 1103. Finalmente, se muestran algunos resultados experimentales representativos del desempeño del algoritmo de control propuesto en el prototipo UPS.

### SUMMARY

In this thesis the control of an uninterruptible power supply (UPS) is investigated using a combined measurement of capacitor and load currents in the same current sensor arrangement. The purpose of this combined measurement is, reaching a similar performance as that obtained in a capacitor current based controller, and obtain an estimate of the inductor current for security purposes.

A controller based on the combined current measurement is proposed to compensate for unbalance and harmonic distortion on the load. Adaptation is included to cope with uncertainties in the parameters of the system. It is shown that after transformations, the proposed controller gets a simple and practical form that includes a bank of resonant filters which is in agreement with the internal model principle. The controller is based on a frequency domain description of the periodic disturbances, which include both symmetric components, namely, the negative and positive sequence, thus, allowing the treatment under unbalance operation as well. As a consequence, the controller compensates only for a selected group of harmonic components. A simple estimator for the inductor current used for protection purposes only is also proposed. The inductor current estimate is obtained in terms of the combined and the capacitor currents. Since the combined current depends directly on the current load, the estimator responds very fast to an over current in the load.

The thesis includes the design and construction of a 1.5 KVA three-phase threewire UPS prototype to experimentally test the proposed controller and estimator. The prototype contains all sensors and signal conditioners as well as the required protections, providing galvanic isolation between the power stage and the control stage, for a safe operation. The experimental results obtained in the prototype are presented here to assess the performance of the proposed algorithm.

## CONTENTS

| 1. | Intro | oduction                                                                    | 1  |

|----|-------|-----------------------------------------------------------------------------|----|

| 2. | Prol  | blem formulation                                                            | 6  |

|    | 2.1   | System description                                                          | 6  |

|    | 2.2   | Mathematical model                                                          | 8  |

|    | 2.3   | Control objective and main assumptions                                      | 11 |

| 3. | Prop  | posed controller                                                            | 13 |

|    | 3.1   | Introduction                                                                | 13 |

|    | 3.2   | Controller design - the known parameters case $\ . \ . \ . \ . \ . \ . \ .$ | 14 |

|    | 3.3   | Controller design - the unknown parameters case                             | 15 |

|    | 3.4   | Disturbance rejection                                                       | 16 |

|    | 3.5   | Controller simplification                                                   | 17 |

|    | 3.6   | Estimation of the inductor current $i_L$                                    | 20 |

| 4. | Phy   | sical implementation                                                        | 21 |

|    | 4.1   | Introduction                                                                | 21 |

|    | 4.2   | Power stages                                                                | 22 |

|    |     | 4.2.1    | Three-phase three-wire UPS system                                          | 22 |

|----|-----|----------|----------------------------------------------------------------------------|----|

|    |     | 4.2.2    | Distorted unbalanced load                                                  | 24 |

|    |     | 4.2.3    | Load switches                                                              | 26 |

|    | 4.3 | Sensor   | rs and signal conditioning stages                                          | 27 |

|    |     | 4.3.1    | Combined current sensor arrangement                                        | 27 |

|    |     | 4.3.2    | Capacitor voltage sensor                                                   | 28 |

|    |     | 4.3.3    | Limiting voltage interface card                                            | 31 |

|    |     | 4.3.4    | Control interface                                                          | 32 |

| 5. | Exp | eriment  | tal results                                                                | 35 |

|    | 5.1 | Introd   | luction                                                                    | 35 |

|    | 5.2 | Discus   | ssion on the resonant filters implementation $\ldots \ldots \ldots \ldots$ | 36 |

|    | 5.3 | Steady   | y state responses                                                          | 38 |

|    | 5.4 | Transi   | ient responses                                                             | 42 |

| 6. | Con | cluding  | remarks                                                                    | 44 |

|    | Ap  | pendix . | A                                                                          | 46 |

|    | Bib | liograp  | hy                                                                         | 48 |

# NOTATION

### Frequent Acronyms

| requeme | 10101191115                      |

|---------|----------------------------------|

| AC      | alternating current              |

| ADC     | analog-to-digital converter      |

| ADP     | analogical digital port          |

| BPF     | band pass filter                 |

| CE      | chip enable                      |

| DC      | direct current                   |

| DSP     | digital signal processor         |

| IGBT    | isolated gate bipolar transistor |

| KCL     | Kirchhoff's current law          |

| KVL     | Kirchhoff's voltage law          |

| LC      | inductor-capacitor               |

| LPF     | low pass filter                  |

| LTI     | linear time invariant            |

| OPWM    | optimum pulse width modulation   |

| PWM     | pulse width modulation           |

| SPWM    | sine pulse width modulation      |

| RMS     | root mean square                 |

| THD     | total harmonic distortion        |

| UPS     | uninterruptible power supplies   |

| VSI     | voltage source inverter          |

|         |                                  |

# Most common mathematical symbols

| $\mathbb{R}$   | field of real numbers                                     |

|----------------|-----------------------------------------------------------|

| ${\rm I\!R}^n$ | linear space of ordered <i>n</i> -tuples in ${\rm I\!R}.$ |

Notation

| $\stackrel{\triangle}{=}$     | "defined as"                                                                            |

|-------------------------------|-----------------------------------------------------------------------------------------|

| $(\cdot)^T$                   | transpose operator                                                                      |

| $(\cdot)^{-1}$                | inverse operator                                                                        |

| t                             | time, $t \in \mathbb{R}_+$                                                              |

| $\frac{d}{dt}, (\dot{\cdot})$ | differentiation operator                                                                |

| $(\cdot)_k^p,$                | k-th harmonic coefficients for the positive sequence representation                     |

| $(\cdot)_k^n$                 | k-th harmonic coefficients for the negative sequence representation                     |

| ${\mathcal J}$                | the skew symmetric matrix $\begin{bmatrix} 0 & -1 \\ 1 & 0 \end{bmatrix}$               |

| $e^{(\cdot)}$                 | (natural, matrix) exponential function                                                  |

| $e^{\mathcal{J}(\cdot)}$      | the $2 \times 2$ rotation matrix                                                        |

|                               | $\begin{bmatrix} \cos(\cdot) & -\sin(\cdot) \\ \sin(\cdot) & \cos(\cdot) \end{bmatrix}$ |

| $(\hat{\cdot})$               | estimate of $(\cdot)$                                                                   |

| $(\tilde{\cdot})$             | error between a quantity and its reference                                              |

|                               | $(\cdot) - (\cdot)_d, \ \hat{(\cdot)} - (\cdot)$                                        |

| $(\cdot)^*$                   | desired external references                                                             |

### Frequently used variables

| : | switching sequence $\forall i \in \{1, 2, 3\}$  |

|---|-------------------------------------------------|

| : | duty cycle $\forall i \in \{1, 2, 3\}$          |

| : | control signal $\forall i \in \{1, 2, 3\}$      |

|   | inductance                                      |

|   | capacitance                                     |

|   | voltage source                                  |

|   | weights for $i_C$ and $i_0$ , resp.             |

|   | inductor currents, $\forall i \in \{1, 2, 3\}$  |

|   | capacitor currents, $\forall i \in \{1, 2, 3\}$ |

|   | load current, $\forall i \in \{1, 2, 3\}$       |

|   | combined current, $\forall i \in \{1, 2, 3\}$   |

|   | control parameters                              |

|   | fundamental frequency                           |

|   | :                                               |

### LIST OF FIGURES

| 1.1 | Current sensor array to obtain the combined current                                                                                                                                                               | 4  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Block diagram of an UPS system.                                                                                                                                                                                   | 7  |

| 2.2 | UPS inverter system                                                                                                                                                                                               | 8  |

| 3.1 | Block diagram of the proposed controller                                                                                                                                                                          | 19 |

| 3.2 | Block diagram of the conventional controller                                                                                                                                                                      | 19 |

| 4.1 | General scheme of the UPS system with proposed control and instru-<br>mentation stages                                                                                                                            | 23 |

| 4.2 | Three-phase three-wire UPS system.                                                                                                                                                                                | 24 |

| 4.3 | Distorted unbalanced load                                                                                                                                                                                         | 25 |

| 4.4 | Load current (only one phase): (top) the current signal $i_{01}$ in the time domain (x-axis 200 ms/div, y-axis 5 A/div) and (bottom) its corresponding frequency spectrum (x-axis 62.5 Hz/div, y-axis 20 dB/div). | 25 |

| 4.5 | Electric circuit of the load switches                                                                                                                                                                             | 26 |

| 4.6 | Electric circuit of the combined current sensor                                                                                                                                                                   | 28 |

| 4.7 | Electric circuit of the combined current sensor                                                                                                                                                                   | 29 |

| 4.8 | Electric circuit of the capacitor voltage sensor                                                                                                                                                                  | 30 |

| 4.9  | Electric circuit of the capacitor voltage sensor                                                                                                                                                                                                                                                                         | 30      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 4.10 | Electric circuit of voltage limiter.                                                                                                                                                                                                                                                                                     | 31      |

| 4.11 | Picture of the voltage limiter card.                                                                                                                                                                                                                                                                                     | 32      |

| 4.12 | Electric circuit of the control interface.                                                                                                                                                                                                                                                                               | 34      |

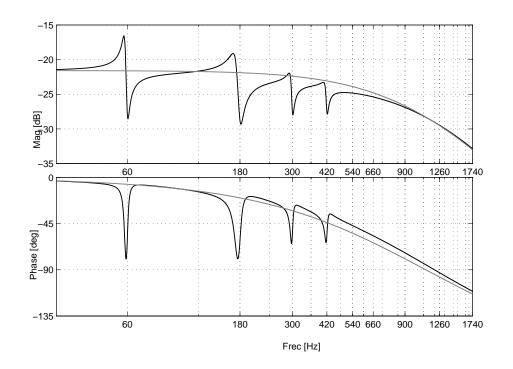

| 5.1  | Bode plot of the error dynamics $(-\overline{\phi} \mapsto \tilde{v}_C)$ using the proposed con-<br>troller (black) with harmonic compensation, and (gray) without the<br>harmonic compensation: (top) Magnitude (x-axis in [Hz], y-axis in<br>[dB]) and (bottom) phase shift (x-axis in [Hz], y-axis in [deg]) $\ldots$ | 37      |

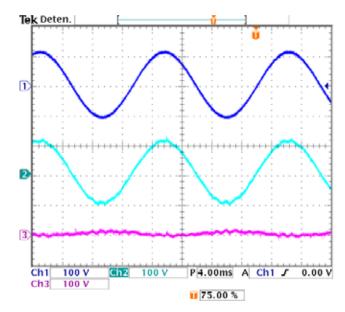

| 5.2  | Output voltage steady state response (only one phase) (from top to <b>bottom</b> ) The reference voltage $v_C^*(t)$ , the actual output voltage $v_C(t)$ , and the error $\tilde{v}_C(t)$ (x-axis 4 ms/div, y-axis 100 V/div)                                                                                            | 38      |

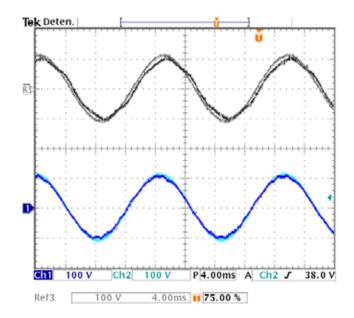

| 5.3  | Output voltage steady state response $v_C(t)$ in black, and corresponding<br>reference $v_C^*(t)$ in gray (only one phase). <b>(top)</b> Conventional controller<br>based on $i_C$ measurements, and <b>(bottom)</b> proposed controller with<br>harmonic compensation (x-axis 4 ms/div, y-axis 100 V/div)               | 39      |

| 5.4  | Frequency spectrum of the output voltage $v_C(t)$ (top) Conventional<br>controller based on $i_C$ measurements, and (bottom) proposed con-<br>troller with adaptable-based harmonic compensation (x-axis 62.5 Hz/div,<br>y-axis 20 dB/div)                                                                               | 40      |

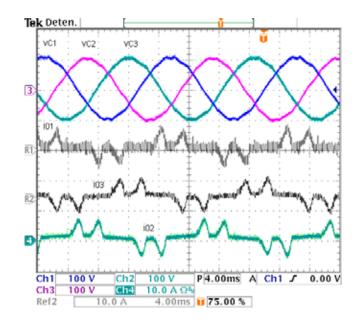

| 5.5  | (top plot) Steady state response of the three output voltages $v_{C1}$ , $v_{C2}$ , $v_{C3}$ (x-axis 4 ms/div, y-axis 100 V/div) and (three bottom plots) distorted and unbalanced load currents $i_{01}$ , $i_{02}$ , $i_{03}$ (x-axis 4 ms/div, y-axis 10 A/div).                                                      | 3<br>41 |

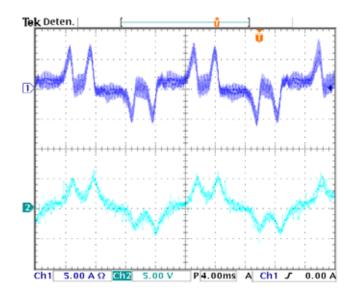

| 5.6  | (top) Actual inductor current $i_L$ (x-axis 4 ms/div, y-axis 5 A/div) and (bottom) its estimate $\hat{i}_L$ (x-axis 20 ms/div, y-axis 5 V/div) (only one phase).                                                                                                                                                         | 41      |

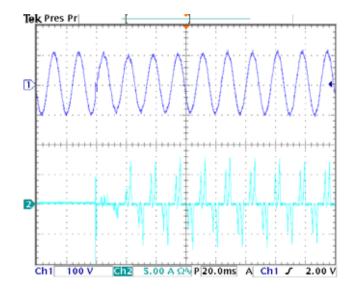

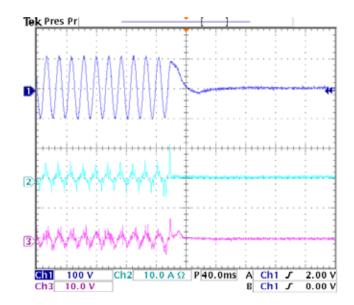

| 5.7 | Transient responses during the connection of the nonlinear and un-                     |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | balanced load. (top) The output voltage $v_C$ (x-axis 20 ms/div, 100                   |    |

|     | V/div) and (bottom) load current $i_0$ (x-axis 20 ms/div, y-axis 5 A/div).             | 42 |

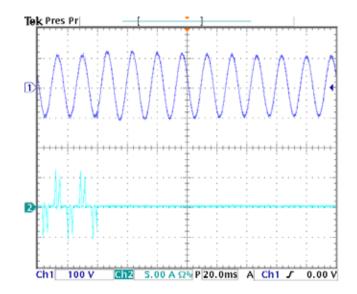

| 5.8 | Transient responses during the disconnection of the nonlinear and un-                  |    |

|     | balanced load current. (top) The output voltage $v_C$ (x-axis 20 ms/div,               |    |

|     | 100 V/div) and (bottom) load current $i_0$ (x-axis 20 ms/div, y-axis 5                 |    |

|     | A/div)                                                                                 | 43 |

| 5.9 | Turn off process due to a load current amplitude exceeding the upper                   |    |

|     | limit fixed at 8 A. (from top to bottom) The output voltage $v_C$                      |    |

|     | (x-axis 40 ms/div, 100 V/div) actual inductor current $i_L$ (x-axis 40                 |    |

|     | ms/div, y-axis 10 A/div) and (bottom) its estimate $\hat{i}_L$ (x-axis 40              |    |

|     | ms/div, y-axis 10 V/div) (only one phase)                                              | 43 |

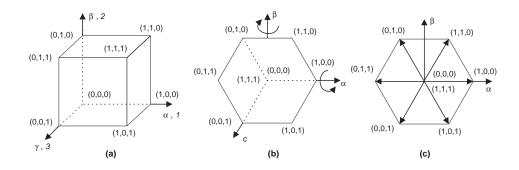

| A.1 | (a) Space vectors in 123-coordinates, (b) rotations to the transformed                 |    |

|     | 123-coordinates into $\alpha\beta\gamma$ -coordinates, and (c) resulting space vectors |    |

|     | in $\alpha\beta\gamma$ -coordinates.                                                   | 47 |

|     |                                                                                        |    |

# LIST OF TABLES

| 2.1 | Parameters of the UPS system                                                                     | 9  |

|-----|--------------------------------------------------------------------------------------------------|----|

| 4.1 | Devices and parameters of the power stages                                                       | 27 |

| 4.2 | Devices and parameters of the combined current sensor                                            | 29 |

| 4.3 | Devices and parameters of the capacitor voltage sensor                                           | 31 |

| 4.4 | Devices and parameters used in the voltage limiter                                               | 32 |

| 4.5 | Devices and parameters used in the control interface                                             | 33 |

| 5.1 | Comparison of the THD reached with the proposed controller and with the conventional controller. | 40 |

|     |                                                                                                  | 10 |

### 1. INTRODUCTION

In recent years uninterruptible power supplies (UPS) are being used more and more to provide emergency power to critical loads such as airline computers, life-support systems in hospitals and communication systems, among others. These systems provide protection against power outages as well as voltage regulation during power line over and under voltage conditions. The UPS systems are also excellent in terms of suppressing incoming line transients and harmonic disturbances. The growing applications and demands on UPSs has pushed the designers to produce systems with stricter specifications, such as, better voltage regulation, lower total harmonic distortion (THD), lower output impedance, better transient response, operation under nonlinear/distorted unbalanced loads and robustness to parametric uncertainties. Clearly, the problem of designing an appropriate UPS control strategy to fulfill all these stricter requirements has become more challenging.

This growing importance of UPS systems has motivated a flourishing development of different control strategies found in the literature, such as: deadbeat control [1], [2], [3], [4], sliding mode control [5], [6], [7], repetitive control [8], [9], [10], adaptive control [11], [12] and many others. Although these techniques are able to ensure good results under large signal disturbance, the THD on the output voltage due to nonlinear loads can still be quite high, especially in high power applications. Perhaps one of the most appealing techniques is the deadbeat control [1], [2], [3], [4], which is a discrete time control technique able to reduce the state variable errors to zero in a finite number of sampling steps, giving a faster dynamic response for digital implementation. Extensive research has also focused on different strategies aimed to eliminate periodic disturbances, such as repetitive-based controllers [8], [9], [10], and adaptive control [11], [12].

In the beginning, a simple output voltage feedback loop accompanied with a sine pulse width modulation (SPWM) scheme [13] was proposed as an easy solution to obtain cleaner sinusoidal output voltage. In this technique, the load voltage is compared with a reference sinusoidal voltage waveform and the difference in amplitude is used to control the modulating signal in the control circuit of the power inverter. A more advanced technique employed a programmed optimum pulse width modulation (OPWM) scheme that was based on the harmonic elimination technique [14]. These schemes have shown to perform well with linear loads. However, with nonlinear loads those pulse width modulation (PWM) based schemes do not guarantee low distortion of the load voltage. To overcome this drawback, a real-time feedback control scheme using dead-beat control was proposed later in [2]. This technique employed the capacitor voltage and its derivative in a control algorithm to calculate the duration of the ON/OFF states of the inverter switching devices. The aim of this approach is that the capacitor voltage can reach the reference voltage at the next sampling time. Although this technique has been successfully implemented in single- and three-phase applications, it has shown the following drawbacks: 1) it is complex to implement; 2) it is sensitive to parameter variations; and 3) its control algorithm requires the estimation of the load parameters. In [15], the authors proposed a new single phase UPS with a dead beat current minor loop using the inductor current, and a voltage major loop using the capacitor voltage. The authors then extended the results with the dead beat current minor loop to the three phase inverters in [1]. Subsequently, the capacitor voltage and the inductor current have been frequently used as the feedback control signals in many different control schemes, such as, adaptive control [11], [12], sliding mode control [6], [7] and others. Perhaps the main advantage of using the inductor current approach is the facility to detect any anomaly arising in the load current, for instance a short circuit. However, this current is polluted with the load current distortion, causing a defective disturbance rejection and output voltage tracking.

To overcome such disadvantages it was proposed a new approach based on the measurements of the current in the capacitor filter, instead of the inductor current.

#### Introduction

In [16] the capacitor current is used as the feedback variable in a two-switch inverter circuit topology to achieve a sinusoidal capacitor current. An outer voltage control loop is also incorporated for to compensate for imperfections in the implementation of the current control and thus guaranteeing load voltage regulation. More recent works using the capacitor current approach [17], [18], [19], [20] have confirmed that, the performance of UPS can be considerably improved if the capacitor current is effectively controlled. This is clear from the fact that while the output voltage is typically the controlled waveform, its time derivative is proportional to the capacitor current. It has been shown as well that a capacitor current feedback topology will exhibit better dynamic stiffness (inverse to the output impedance), a key metric in UPSs performance, than that of a controller with inductor current feedback. Moreover, since the capacitor current is small and alternate in nature, it may be sensed with a small and inexpensive current transformer. Thus, it can be considered a low cost alternative that has the potential to exhibit outstanding performance. However, since neither the load current nor the inductance current are measured, this controller is unable to detect, in a relatively short period of time, any anomaly arising on the load side. For instance, if a short circuit appears the capacitor current is maintained, theoretically, at the desired reference while the inductance current will grow unlimited in a short time with the unavoidable destructive effects.

In general terms, we can say that the implementation of the proposed controllers usually involves measurements of the output voltage and either, the inductor currents [3], [11], [12], or the capacitor currents [17], [18], [20] and in some cases, they even require measurements of the load current [19] with the idea of attenuating the effect of disturbances in the load. The capacitor voltage is introduced in these controllers in a second voltage loop to alleviate imperfections in the response due to parameter uncertainties and load disturbances. Therefore, based on the current signals used in the feedback control, we can distinguish two types of controllers: inductor current based and capacitor current based.

In this work a solution is proposed for the control of an UPS system to overcome such a disadvantage while preserving a good performance and guaranteeing balanced sinusoidal output voltages despite of the presence of nonlinear and unbalanced loads. This solution involves the use of a combined measurement of both load current and

#### Introduction

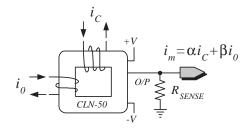

capacitor current in the control loop. This combined measurement is performed in the same sensor as seen in Fig. 1.1, thus preserving the same number of current sensors as in a conventional controller. This will provide a linear combination, i.e., a weighted sum of both currents, which is then used as the feedback variable in the control loop. The current sensor CLN-50 is used for this propose. In the CLN-50 both conductors, the one conducting the capacitor current and the other conducting the load current, have been wired to obtain directly the weighted sum of both currents. Notice that, in the particular case where both weights are fixed to one, this combined current is simply the inductance current. On the other hand, assigning a zero weight to the load current leads to the capacitor current case. So a good performance can be obtained (close to the capacitor current based controller) if a smaller weight is assigned to the load current compared to the one for the capacitor current. It is shown that a simple estimator for the inductor current can now be implemented from the information contained in the combined current and the capacitor voltage measurements, plus the knowledge of the weights used. Although this estimate depends on the value of the capacitance, this signal is not used in the controller design, but its use is reserved for safety purposes, therefore the use of a nominal value for the capacitance is enough.

Fig. 1.1: Current sensor array to obtain the combined current.

Adaptive refinements have also been added to the proposed controller to cope with parametric uncertainties and periodic disturbances. By using the frequency domain descriptions of some unknown signals (disturbances), the solution presented here is able to perform precise voltage tracking despite of the presence of distorting loads. It reduces the effects of unbalance and harmonic distortion, likewise to other frequency domain techniques, such as repetitive control [8], [9], [10], and synchronous frame harmonic control [21]. For such purpose, the system dynamics is obtained using stationary frame quantities and the load currents (disturbance) with slowly varying

#### Introduction

phasors. Both symmetric sequence components, positive and negative, are considered so that the unbalance operation can be treated.

In the terminology of control theory, the proposed controller performs a partial inversion of the system and adds the needed damping. The resulting system contains a disturbance term due to the uncertainty in the system parameters which is addressed via adaptation. Due to the complexity of this controller, we also propose a simple rotational transformations so that the computation complexity can be significantly reduced. Similarly to other frequency domain techniques, a group of selected harmonics are considered for compensation, and thus the proposed approach can be classified as selective since only a selected set of harmonics is targeted for compensation. The solution proposed here is based on a new, more rigorous theoretical framework, since only the disturbance terms are represented in the frequency domain and no approximations are needed for final control implementation. Finally, the proposed control scheme has been implemented and tested in a 1.5 KVA three phase inverter prototype and the experimental results are presented.

This thesis report is organized as follows. In Chapter 2, the formulation of the problem is established. In particular, the system configuration, the mathematical model, and the control objective are explained. In Chapter 3, the proposed controller is presented. In Chapter 4, all stages of the UPS system physical implementation are explained in detail. In Chapter 5, the experimental results are shown. Finally, in Chapter 6, some concluding remarks are given.

### 2. PROBLEM FORMULATION

### 2.1 System description

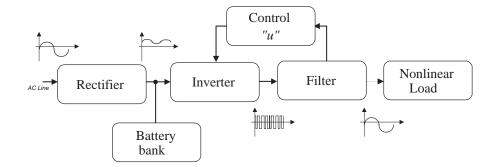

THE most popular setup of an UPS system is shown in its block diagram form of Fig. 2.1. The rectifier is used for converting single-phase or three-phase alternating current (AC) input into direct current (DC), which supplies power to both the voltage source inverter (VSI) and the battery bank. The VSI produces a periodical signal composed mainly of a fundamental component. The output voltage of the VSI is filtered prior to be applied to the load. An inductance-capacitor (LC) filter is typically used. This filter acts as a low pass filter (LPF) that eliminates high order harmonics leaving an almost pure sinusoidal waveform. The completed UPS system includes also stages of protection . As previously mentioned, the control signal may involve measurements of the output voltage and either, the inductor or the capacitor current measurements. Most of the material presented here has been extracted from [22] and [23].

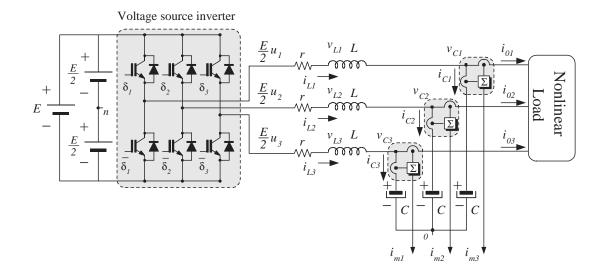

In this work, the three-phase three-wire UPS topology shown in Fig. 2.2 is used. This is perhaps the most popular setup of a UPS system found in the power electronics literature [22]. This system includes different stages, such as, rectifier, battery bank, inverter, etc. The rectifier is used to convert single-phase or three-phase AC voltage into DC voltage, which supplies power to both the VSI and the battery bank. The VSI produces a PWM signal composed mainly of a fundamental component. The output voltage of the VSI is filtered prior to be applied to the load. An LC filter is

Fig. 2.1: Block diagram of an UPS system.

typically used. This filter acts as a LPF that eliminates high order harmonics due to the switching process, thus leaving an almost pure sinusoidal waveform. The overall UPS system includes also different protection circuits. As previously mentioned, the control signal may involve measurements of the output voltage and either, the inductor or the capacitor current measurements, therefore the appropriate sensors should also be provided. The control of such system is usually implemented in a digital signal processor (DSP) based board, where also the signal conditioners and operational manoeuvres to start and stop the system safely are included.

The inverter is evidently the most important part in an UPS since the good performance of the overall system will strongly depend on how well the inverter is designed and controlled. Therefore, this work concentrates on the control design for a given UPS inverter topology. There are of course different topologies for UPS, in this work the three-phase three-wire inverter shown in Fig.2.2 is studied. This topology is composed of an input voltage source, three legs (one for each phase) connected to an LC filter with the aim to generate an almost sinusoidal output voltage. Each leg consists of a cascade connection of two IGBTs, each with an antiparallel (freewheeling) diode. The IGBTs are turned on by applying a 15V signal between gate and emitter, and they are turned off with a -15V signal. The control signal applied to the gate of a given IGBT is referred as the switching sequence, which is generated in a SPWM. A drive is placed in between each SPWM and gate to reinforce the SPWM signal. Considering the Fig.2.2, the switching sequences are referred as  $\delta_i \in \{0, 1\} \forall i \in \{1, 2, 3\}$ . Notice that, if  $\delta_i = 1$  for some  $i \in \{1, 2, 3\}$  then, the respective upper IGBT is activated and if  $\delta_i = 0$  for some  $i \in \{1, 2, 3\}$  then, the respective lower IGBT is activated.

#### 2.2 Mathematical model

The modeling process starts by considering that the SPWM operates at a relatively high switching frequency. Based on this assumption, the switching sequence and the duty cycle of the SPWM can be used indistinctly in the mathematical expressions, where the duty cycle is defined as  $d_i \in [0,1]$ ,  $\forall i \in \{1,2,3\}$ . The use of the duty cycle facilitates considerably the control design since this signal is continuous, in contrast with the switching sequence that takes values in a discrete set  $\delta_i \in \{0,1\}$ ,  $\forall i \in \{1,2,3\}$ . This leads to what is referred in the power electronics literature as the average model [24]. Moreover, since most of the signals in the system have an alternate nature, it is very convenient to map the duty ratio signals towards new variables  $u_i$ ,  $\forall i \in \{1,2,3\}$  which take values in the range [-1,1]. This is performed by means of the following transformations  $u_i = 2d_i - 1 \forall i \in \{1,2,3\}$ . These new variables  $u_i$  are consider from now on as the input control signals. Let us apply the

Fig. 2.2: UPS inverter system.

Kirchhoff's Voltage Law (KVL) to the electric diagram shown in Fig.2.2, taking the value of the inductors the same for each branch and assuming that they are linear

, i.e.,  $v_{Li} = L \frac{d}{dt} i_{Li} \forall i \in \{1, 2, 3\}$ , and that without lost of generality the parasitic inductor resistance r can be neglect (see [25]). This yields

$$L\frac{d}{dt}i_{L1} = -v_{C1} + v_{n0} + \frac{E}{2}u_1$$

$$L\frac{d}{dt}i_{L2} = -v_{C2} + v_{n0} + \frac{E}{2}u_2$$

$$L\frac{d}{dt}i_{L3} = -v_{C3} + v_{n0} + \frac{E}{2}u_3$$

(2.1)

where

| L                 | : | inductance                                     |

|-------------------|---|------------------------------------------------|

| C                 | : | capacitance                                    |

| E                 | : | voltage source                                 |

| $v_{n0}$          | : | voltage between $n$ and $0$                    |

| $v_{Ci}$          | : | capacitor voltages $\forall i \in \{1, 2, 3\}$ |

| $u_i \in [-1, 1]$ | : | control signal $\forall i \in \{1, 2, 3\}$     |

| $\alpha,\beta$    | : | weights for $i_C$ and $i_0$ , resp.            |

| $i_{Li}$          | : | inductor currents $\forall i \in \{1, 2, 3\}$  |

| $i_{Ci}$          | : | capacitor currents $\forall i \in \{1, 2, 3\}$ |

| $i_{0i}$          | : | load current $\forall i \in \{1, 2, 3\}$       |

| $i_{mi}$          | : | combined current $\forall i \in \{1, 2, 3\}$   |

|                   |   |                                                |

Table 2.1: Parameters of the UPS system.

Since three-phase three-wire topology is used, then the sum of the three inductor currents is zero. Moreover, it can also be assumed that the sum of the three capacitor voltages is zero. This permits to solve for  $v_{n0}$  from (2.1) giving the following expression

$$v_{n0} = -\frac{E}{2} \left( \frac{u_1 + u_2 + u_3}{3} \right) \tag{2.2}$$

Substituting (2.2) in (2.1) yields the following dynamical expressions

$$L\frac{d}{dt}i_{L1} = -v_{C1} + \frac{E}{2}\left(\frac{2}{3}u_1 - \frac{1}{3}u_2 - \frac{1}{3}u_3\right)$$

$$L\frac{d}{dt}i_{L2} = -v_{C2} + \frac{E}{2}\left(-\frac{1}{3}u_1 + \frac{2}{3}u_2 - \frac{1}{3}u_3\right)$$

$$L\frac{d}{dt}i_{L3} = -v_{C3} + \frac{E}{2}\left(-\frac{1}{3}u_1 - \frac{1}{3}u_2 + \frac{2}{3}u_3\right)$$

which can be rewritten in matrix form as

$$L\frac{d}{dt}i_{L123} = -v_{C123} + \frac{E}{2}Bu_{123}$$

(2.3)

where  $i_{L123} = \begin{bmatrix} i_{L1}, i_{L2}, i_{L3} \end{bmatrix}^T$ ,  $v_{C123} = \begin{bmatrix} v_{C1}, v_{C2}, v_{C3} \end{bmatrix}^T$ ,  $u_{123} = \begin{bmatrix} u_1, u_2, u_3 \end{bmatrix}^T$ and the matrix *B* is given by

$$B = \frac{1}{3} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix}$$

Applying the Clarke's transformation (see Appendix A) to (2.3) yields the following model in terms of the (fixed frame)  $\alpha\beta$ -coordinates

$$L\frac{d}{dt}i_{L\alpha\beta} = -v_{C\alpha\beta} + \frac{E}{2}u_{\alpha\beta}, \qquad (2.4)$$

where we have used the fact that  $TBT^{-1} = \text{diag}\{1, 1, 0\}$ .

**Remark 2.2.1** Notice that the third coordinate  $\gamma$  has been neglected as the system considered here is a three wire topology.

Now, applying the Kirchhoff's current law (KCL), to the system shown in Fig. 2.2, the following system is obtained

$$C \frac{d}{dt} v_{C1} = i_{L1} - i_{01}$$

$$C \frac{d}{dt} v_{C2} = i_{L2} - i_{02}$$

$$C \frac{d}{dt} v_{C3} = i_{L3} - i_{03},$$

(2.5)

or simply

$$C\frac{d}{dt}v_{C123} = i_{L123} - i_{0123} \tag{2.6}$$

where  $v_{C123} = \begin{bmatrix} v_{C1}, v_{C2}, v_{C3} \end{bmatrix}^T$ ,  $i_{L123} = \begin{bmatrix} i_{L1}, i_{L2}, i_{L3} \end{bmatrix}^T$  and  $i_{0123} = \begin{bmatrix} i_{01}, i_{02}, i_{03} \end{bmatrix}^T$ .

After application of Clarke's transformation to (2.6), the dynamics of the capacitor voltage is expressed in terms of the fixed frame coordinates as follows

$$C\frac{d}{dt}v_{C\alpha\beta} = i_{L\alpha\beta} - i_{0\alpha\beta}, \qquad (2.7)$$

Summarizing, the complete dynamics of the three-phase three-wire UPS system in the fixed reference frame, i.e., in  $\alpha\beta$ -coordinates, is given by expressions (2.4) and (2.7). In the rest of the thesis, the subscripts  $\alpha$  and  $\beta$  are omitted to simplify the notation and to avoid confusions with the weight parameters  $\alpha$  and  $\beta$ .

### 2.3 Control objective and main assumptions

The dynamics (2.4) and (2.7) can be rewritten in terms of  $i_C$  in the fixed frame coordinates as

$$L\frac{di_C}{dt} = -v_C + \frac{E}{2}u - L\frac{di_0}{dt}$$

$$(2.8)$$

$$C\frac{dv_C}{dt} = i_L - i_0 = i_C \tag{2.9}$$

$$i_m = \alpha i_C + \beta i_0, \qquad (2.10)$$

where  $i_L = i_C + i_0$  has been used. Notice that the combined current  $i_m$  and the capacitor voltage  $v_C$  are the only available signals.

For the controller design purposes, the following assumptions are considered:

- A1. Parameters L, C and E are all assumed to be unknown constants.

- A2. Signal u, representing the actual control, is a continuous signal proportional to the duty ratio of a SPWM switching at a relatively high frequency.

- A3. Parameters  $\alpha$  and  $\beta$  are the known weights that form the combined current  $i_m = \alpha i_C + \beta i_0$ .

- A4. The current  $i_0$  is an unbalanced periodic signal which can be expressed as the combination of a fundamental component (at a fixed frequency  $w_0$ ) and its harmonics of higher order. This means that  $i_0$  can be represented as a Fourier series of the form

$$i_0 = \sum_{k \in \mathcal{H}} \left( e^{\mathcal{J}kw_0 t} I^p_{0,k} + e^{-\mathcal{J}kw_0 t} I^n_{0,k} \right)$$

(2.11)

2.2.3. Control objective and main assumptions

$$e^{\mathcal{J}w_0t} = \begin{bmatrix} \cos(w_0t) & -\sin(w_0t) \\ \sin(w_0t) & \cos(w_0t) \end{bmatrix} , \quad \mathcal{J} = \begin{bmatrix} 0 & -1 \\ 1 & 0 \end{bmatrix},$$

where  $w_0$  represents the fundamental frequency and vectors  $I_{0,k}^p, I_{0,k}^n \in \mathbb{R}^2$  are the k-th harmonic coefficients for the positive and negative sequence representation, which are assumed as unknown constants (or slowly varying);  $\mathcal{H} =$  $\{1, 3, 5, 7, 11, ...\}$  is the set of multiples of the harmonic components considered. Its time derivative, used later in the control derivation, is given by

$$\frac{di_0}{dt} = \sum_{k \in \mathcal{H}} \mathcal{J}kw_0 \left( e^{\mathcal{J}kw_0 t} I^p_{0,k} - e^{-\mathcal{J}kw_0 t} I^n_{0,k} \right)$$

(2.12)

The *control objective* can now be stated as follows:

The capacitor voltages vector should be forced to track a balanced voltage reference given by

$$v_C^* = e^{\mathcal{J}w_0 t} \begin{bmatrix} V_d \\ 0 \end{bmatrix} = V_d \begin{bmatrix} \cos(w_0 t) \\ \sin(w_0 t) \end{bmatrix}$$

which is a purely balanced sinusoidal vector signal of amplitude  $V_d$ , i.e., it is composed by a positive sequence fundamental component only. Moreover, this tracking should be guaranteed in spite of the presence of harmonic disturbances. Thus, the control objective implicitly includes two problems: the reference tracking of the fundamental component and disturbance attenuation of the output voltage to higher order harmonics produced by the distorted load current.

The equilibrium point of the overall system by forcing  $v_C^* = e^{\mathcal{J}w_0 t} [V_d, 0]^\top$  is given by

$$\bar{i}_m = \alpha \mathcal{J} w_0 C v_C^* + \beta i_0 \quad , \quad \bar{v}_C = v_C^* \tag{2.13}$$

Notice that, to guarantee perfect voltage tracking it suffices to force the combined current  $i_m$  to follow a reference signal  $\bar{i}_m$  given by (2.13), which, unfortunately, depends on the unavailable signal  $i_0$  and unknown parameter C. Here, and in what follows  $(\cdot)^*$  will be used to denote references and  $\overline{(\cdot)}$  for values in the equilibrium.

Notice that the time derivative of the voltage reference, that is used later in the design process, is given by  $\dot{v}_C^* = \mathcal{J} w_0 v_C^*$ .

### 3. PROPOSED CONTROLLER

### 3.1 Introduction

$\neg$ HE design of the proposed controller is based on the combined measurement of capacitor and load currents in the same current sensor arrangement. As pointed out before, the idea is, on the one hand, to reach a similar performance as that obtained in a capacitor current based controller, and on the other hand, to obtain a simple estimator for the inductor current which is used for security purposes only. A key idea in the design process is the description of the periodic disturbances in terms of their frequency domain variables, which include both symmetric components, namely, the negative and positive sequence for each harmonic component, thus, allowing the treatment of unbalance operation. By using the frequency domain descriptions of the disturbance signals, the solution presented here is able to perform precise voltage tracking despite of the presence of distorting loads. In terms of control theory, the proposed controller realizes a partial inversion of the system, and adds the needed damping. The resulting system contains a disturbance term due to the uncertainty in the system parameters which is then addressed via adaptation. An important observation is that, thanks to appropriate rotations, it is possible to reduce considerably the complexity of the proposed controller. Its final expression is very close to the conventional one, to which a bank of resonant filters have been added. The latter is constitutes one of the major contributions of the present work. It is interesting to mention that the introduction of the bank of resonant filters in agreement with the internal model principle. Moreover, the proposed controller compensates only for a selected group of harmonic components, and thus, belongs to the family of selective control algorithms.

#### 3.2 Controller design - the known parameters case

Let us write the dynamics of the system (2.8)-(2.9) in terms of the combined current  $i_m$  (2.10); this yields

$$L\frac{di_m}{dt} = -\alpha v_C - (\alpha - \beta)L\frac{di_0}{dt} + \frac{\alpha E}{2}u$$

(3.1)

$$\alpha C \frac{dv_C}{dt} = i_m - \beta i_0 \tag{3.2}$$

Notice that, the above system is a linear time invariant (LTI) system which is clearly controllable according to standard theory (see [26]).

The controller design is based on the following expression for the error model

$$L\frac{d\tilde{i}_m}{dt} = -\alpha \left(\tilde{v}_C + v_C^*\right) + \alpha \frac{E}{2}u - (\alpha - \beta)L\frac{di_0}{dt} - L\frac{d\bar{i}_m}{dt}$$

$$= \alpha \left(\frac{E}{2}u - \tilde{v}_C - v_C^*\right) - (\alpha - \beta)L\frac{di_0}{dt} - L\frac{d\bar{i}_m}{dt}$$

(3.3)

$$\alpha C \frac{d\tilde{v}_C}{dt} = \tilde{i}_m + \bar{i}_m - \beta i_0 - \alpha C \frac{dv_C^*}{dt}$$

$$= \tilde{i}_m$$

(3.4)

where the error variables are defined as  $\tilde{v}_C \stackrel{\triangle}{=} v_C - v_C^*$  and  $\tilde{i}_m \stackrel{\triangle}{=} i_m - \bar{i}_m$ , with  $v_C^*$ , and  $\bar{i}_m$  as defined in Chapter 2, and the fact that  $\frac{dv_C^*}{dt} = \mathcal{J}w_0v_C^*$  are used.

In the case of known parameters, i.e., with  $L, C, i_0$  and  $\frac{di_0}{dt}$  all known, the following controller that can be proposed to guarantees asymptotic stable tracking, that is,  $\tilde{v}_C \to 0$  as  $t \to \infty$ .

$$\frac{\alpha E}{2}u = -R_1\tilde{i}_m - R_2\tilde{v}_C + (\alpha - \beta)L\frac{di_0}{dt} + \alpha v_C^* + L\frac{d\bar{i}_m}{dt},$$

where  $R_1$  and  $R_2$  are two positive design parameters to add the required damping. The design of the previous controller can be resumed as follows. First, a copy of the system is constructed and evaluated in the desired steady state. Second, we add to that expression the required damping by feeding back the errors through the gains  $R_1$  and  $R_2$ . Finally, from the resulting expression, we solve for the controller u. See [27] for further details in the passivity-based control design technique. Notice that most terms of the controller above are intended to cancel the corresponding terms in the error model.

### 3.3 Controller design - the unknown parameters case

Now, in the case that the system parameters and disturbances are unknown, the following controller based on the structure of the above controller is proposed.

$$\frac{\alpha E}{2}u = -R_1(i_m - i_m^*) - R_2 \tilde{v}_C + (\alpha - \beta)\hat{L}\frac{d\hat{i}_0}{dt} + \alpha v_C^* + \hat{L}\frac{di_m^*}{dt}$$

(3.5)

where  $\widehat{(\cdot)}$  is used to represent the estimated value of  $(\cdot)$ , and we have replaced  $\overline{i}_m$  by  $i_m^* \triangleq \alpha \mathcal{J} w_0 \hat{C} v_C^* + \beta \hat{i}_0$ , which is a signal used to approximate  $\overline{i}_m$ , since C is a unknown parameter and  $i_0$  is not available. Notice that in this controller all unknown terms have been replaced by their estimates.

The main idea behind the controller design consists in lumping all periodic uncertainties in a single term  $\hat{\phi}$  as follows

$$\frac{\alpha E}{2}u = -R_1 i_m - R_2 \tilde{v}_C + \alpha v_C^* + \hat{\phi}$$

(3.6)

where  $\hat{\phi} = R_1 i_m^* + (\alpha - \beta) \hat{L} \frac{d\hat{i}_0}{dt} + \hat{L} \frac{d\hat{i}_m^*}{dt}$ . The relevance of this representation will be more evident later on.

Direct substitution of (3.5) in the system (3.3)-(3.4) yields the closed loop system

$$\frac{Ld\tilde{i}_m}{dt} = -R_1\tilde{i}_m - (\alpha + R_2)\tilde{v}_C + \underbrace{\left(R_1i_m^* + (\alpha - \beta)\hat{L}\frac{d\hat{i}_0}{dt} + \hat{L}\frac{di_m^*}{dt}\right)}_{\hat{\phi}} \\

-\underbrace{\left(R_1\bar{i}_m + (\alpha - \beta)L\frac{di_0}{dt} + L\frac{d\bar{i}_m}{dt}\right)}_{\bar{\phi}} \\

= -R_1\tilde{i}_m - (\alpha + R_2)\tilde{v}_C + (\hat{\phi} - \bar{\phi}) \tag{3.7}$$

$$\alpha C \frac{dv_C}{dt} = \tilde{i}_m \tag{3.8}$$

where  $\overline{\phi} \stackrel{\triangle}{=} R_1 \overline{i}_m + (\alpha - \beta) L \frac{di_0}{dt} + L \frac{d\overline{i}_m}{dt}$  have been defined.

Notice that this system, referred as the *error dynamics*, is a system LTI perturbed by a periodic disturbance  $(\hat{\phi} - \overline{\phi})$ . Moreover, it is easy to see that the system above satisfy the so called *matching condition*, therefore the perturbation  $\overline{\phi}$  can be cancelled by means of the actual control  $\hat{\phi}$  (see [28]).

#### 3.4 Disturbance rejection

According to (2.11) the periodical signals  $\hat{\phi}$  and  $\overline{\phi}$  can be described as follows

$$\hat{\phi} \stackrel{\Delta}{=} \sum_{k \in \mathcal{H}} \left( \hat{\phi}_k^p + \hat{\phi}_k^n \right) = \sum_{k \in \mathcal{H}} \left( e^{\mathcal{J}w_0 k t} \hat{\Phi}_k^p + e^{-\mathcal{J}w_0 k t} \hat{\Phi}_k^n \right)$$

$$\overline{\phi} \stackrel{\Delta}{=} \sum_{k \in \mathcal{H}} \left( \phi_k^p + \phi_k^n \right) = \sum_{k \in \mathcal{H}} \left( e^{\mathcal{J}w_0 k t} \Phi_k^p + e^{-\mathcal{J}w_0 k t} \Phi_k^n \right)$$

where the vectors  $\Phi_k^p$ ,  $\Phi_k^n \in \mathbb{R}^2$  are the k-th harmonic coefficients for the positive and negative sequence representation of the disturbance  $\overline{\phi}$ , and  $\hat{\Phi}_k^p$ ,  $\hat{\Phi}_k^n$  their corresponding estimates.

As a result the error signal  $\tilde{\phi}=(\hat{\phi}-\overline{\phi})$  can be expressed as

$$\tilde{\phi} \stackrel{\triangle}{=} \sum_{k \in \mathcal{H}} \left( \tilde{\phi}_k^p + \tilde{\phi}_k^n \right) = \sum_{k \in \mathcal{H}} \left( e^{\mathcal{J}w_0 k t} \tilde{\Phi}_k^p + e^{-\mathcal{J}w_0 k t} \tilde{\Phi}_k^n \right)$$

where  $\tilde{\Phi}_k^p \stackrel{\triangle}{=} (\hat{\Phi}_k^p - \Phi_k^p)$  and  $\tilde{\Phi}_k^n \stackrel{\triangle}{=} (\hat{\Phi}_k^n - \Phi_k^n)$  are defined.

The adaptive laws are obtained by following a Lyapunov approach where the proposed energy storage function is

$$W = \frac{\alpha LC |\dot{\tilde{v}}_C|^2}{2} + \frac{(\alpha + R_2) |\tilde{v}_C|^2}{2} + \sum_{k \in \mathcal{H}} \frac{\left[ (\tilde{\Phi}_k^p)^2 + (\tilde{\Phi}_k^n)^2 \right]}{2\gamma_k}$$

(3.9)

where  $\gamma_k, k \in \mathcal{H}$ , are positive design constants.

Its time derivative along the trajectories of (3.8) gives

$$\dot{W} = -\alpha R_1 C \dot{\tilde{v}}_C^2 + \dot{\tilde{v}}_C^\top \sum_{k \in \mathcal{H}} \left[ e^{\mathcal{J}kw_0 t} \tilde{\Phi}_k^p + e^{-\mathcal{J}kw_0 t} \tilde{\Phi}_k^n \right] + \sum_{k \in \mathcal{H}} \frac{\left[ (\dot{\tilde{\Phi}}_k^p)^\top \tilde{\Phi}_k^p + (\dot{\tilde{\Phi}}_k^n)^\top \tilde{\Phi}_k^n \right]}{\gamma_k}$$

which is made negative semidefinite by proposing the following adaptation laws

$$\hat{\Phi}_{k}^{p} = -\gamma_{k}e^{-\mathcal{J}kw_{0}t}\dot{\tilde{v}}_{C} \quad , \quad \hat{\Phi}_{k}^{n} = -\gamma_{k}e^{\mathcal{J}kw_{0}t}\dot{\tilde{v}}_{C} \tag{3.10}$$

where  $\dot{\hat{\Phi}}_{k}^{p} = \dot{\tilde{\Phi}}_{k}^{p}$  and  $\dot{\hat{\Phi}}_{k}^{n} = \dot{\tilde{\Phi}}_{k}^{n}$  since  $\Phi_{k}^{p}$  and  $\Phi_{k}^{n}$  are assumed constant.

Since  $\dot{W} = -\alpha R_1 C \dot{\tilde{v}}_C^2$ , as a first conclusion we have that  $\dot{\tilde{v}}_C \to 0$  and moreover it is bounded. Then invoking standard LaSalle's theorem arguments [29] assuming  $\dot{\tilde{v}}_C \equiv 0$  in the closed loop system (3.7) and (3.8), the invariant set described by  $(\alpha + R_2)\tilde{v}_C = \tilde{\phi}$  is obtained; in addition  $\hat{\Phi}_k^p$ ,  $\hat{\Phi}_k^n$  are constant  $\forall k \in \mathcal{H}$ , which implies in turn that  $\tilde{\phi}$  is a time varying bounded signal. However,  $\tilde{v}_C$  is a constant and bounded signal, therefore, the only possible solution is  $\tilde{v}_C \to 0$  which in turn implies  $\tilde{\phi} \to 0$ , and moreover  $\tilde{\Phi}_k^p \to 0$  and  $\tilde{\Phi}_k^n \to 0$ .

Summarizing, the controller composed by (3.6) and (3.10) guarantees tracking of the capacitor voltage towards its sinusoidal reference despite of the presence of a distorted load current, that is, with disturbance rejection. In what follows it is shown that, by means of suitable rotations, it is possible to reduce considerably the expression and computational effort of the proposed controller, thus facilitating its implementation.

#### 3.5 Controller simplification

To facilitate the implementation of the above controller the following transformations (rotations) are proposed

$$\hat{\phi}_k^p = e^{\mathcal{J}kw_0 t} \hat{\Phi}_k^p \quad , \quad \hat{\phi}_k^n = e^{-\mathcal{J}kw_0 t} \hat{\Phi}_k^n. \tag{3.11}$$

Thus the adaptation laws can be written as

$$\dot{\hat{\phi}}_{k}^{p} = -\gamma_{k}\dot{\tilde{v}}_{C} + \mathcal{J}kw_{0}\hat{\phi}_{k}^{p}$$

(3.12)

$$\dot{\hat{\phi}}_k^n = -\gamma_k \dot{\tilde{v}}_C - \mathcal{J}k w_0 \hat{\phi}_k^n.$$

(3.13)

The transfer function expressions of the adaptation laws are given by

$$\hat{\phi}_k^p = \frac{-\gamma_k s(s + \mathcal{J} k w_0)}{s^2 + k^2 w_0^2} \tilde{v}_C$$

3.3.5. Controller simplification

$$\hat{\phi}_k^n = \frac{-\gamma_k s(s - \mathcal{J}kw_0)}{s^2 + k^2 w_0^2} \tilde{v}_C$$

where s is the complex variable.

Therefore the adaptations are reduced to

$$\hat{\phi}_{k} = \hat{\phi}_{k}^{p} + \hat{\phi}_{k}^{n} = \frac{-2\gamma_{k}s^{2}}{s^{2} + k^{2}w_{0}^{2}}\tilde{v}_{C}

= -2\gamma_{k}\tilde{v}_{C} + \frac{2\gamma_{k}k^{2}w_{0}^{2}}{s^{2} + k^{2}w_{0}^{2}}\tilde{v}_{C} .$$

(3.14)

In conclusion, the final expression for the controller is given by

$$\frac{\alpha E}{2}u = -R_1 i_m - \left(R_2 + 2\sum_{k\in\mathcal{H}}\gamma_k\right)\tilde{v}_C + \alpha v_C^* + \sum_{k\in\mathcal{H}}\frac{2\gamma_k k^2 w_0^2}{s^2 + k^2 w_0^2}\tilde{v}_C.$$

(3.15)

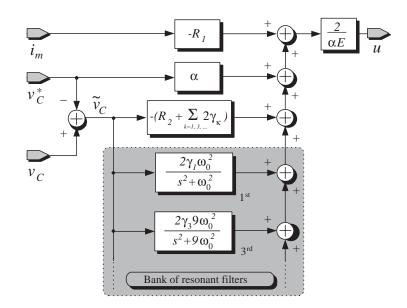

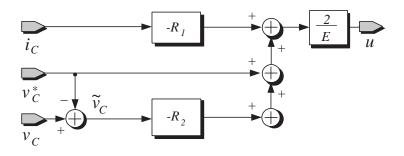

Figure 3.1 presents the block diagram of the final proposed controller (3.15). Notice that this structure is composed of: a proportional term acting over the combined current  $i_m$  aimed to add the required damping; a term  $\alpha$  multiplying the reference voltage  $v_C^*$ , which is intended to keep the natural damping when added to the corresponding term  $\alpha v_C$  appearing in the model description (3.1)-(3.2); a proportional term acting over the voltage error  $\tilde{v}_C$  to improve the required damping, notice that, this term depends on the  $\gamma_k$  value, therefore special care should be taken to update this term when the harmonic compensation is enabled; a bank of resonators of the form  $\frac{2\gamma_k k^2 w_0^2}{s^2 + k^2 w_0^2}$ ,  $\forall k \in \mathcal{H}$  acting over the voltage error  $\tilde{v}_C$ . This bank of resonant filters is dedicated to the harmonic compensation.

For comparison, a simple controller that captures the essence of the multiple reported capacitor current based controllers [17], [18], [20] has been drawn in Fig. 3.2 to exhibit the main differences with respect to the proposed controller. This simple controller is referred in this work as the conventional controller, which is composed of the following terms: a proportional term acting over  $i_C$  to add the required damping; the reference voltage  $v_C^*$ , which is referred as the feedforward term; a proportional term acting over  $\tilde{v}_C$  to add the required damping. Notice that, this controller does not contain a term specifically devoted to the harmonic compensation. Some authors prefer to use  $\tilde{i}_C$  instead of  $i_C$ , for this, they introduce a reference  $i_C^*$  which requires the time derivative of the reference  $v_C^*$ , plus the knowledge of the capacitance. Yet some authors introduce the second time derivative of the capacitor voltage reference affected by the inductance and capacitance with the aim to improve the tracking. But all this terms complicate the controller expression and are very sensitive to system parameters variations. Anyway, none of these proposals solve the disturbance rejection issue stated here.

Fig. 3.1: Block diagram of the proposed controller.

Fig. 3.2: Block diagram of the conventional controller.

## 3.6 Estimation of the inductor current $i_L$

As pointed out before, the aim of the proposed combined current arrangement is the facility to reconstruct the inductor current  $i_L$  which can then be used for protection purposes only. Solving for  $i_L$  from (2.9)-(2.10) yields

$$i_L = \frac{1}{\beta} i_m + \frac{\beta - \alpha}{\beta} i_C \tag{3.16}$$

which unfortunately requires the unaccessible signal  $i_C$ . However, since the capacitor current  $i_C$  is defined as C times the time derivative of the capacitor voltage  $v_C$ , it is possible to estimate  $i_L$  as follows

$$\hat{i}_L = \frac{1}{\beta} \left( \frac{1}{\sigma s + 1} \right) i_m + \frac{\beta - \alpha}{\beta} \left( \frac{Cs}{\sigma s + 1} \right) v_C \tag{3.17}$$

where  $\hat{i}_L$  represents the estimate of  $i_L$ . The idea behind this estimator consists in introducing a LPF with a pole fixed at  $1/\sigma$  on the right hand side of (3.16). This produces a proper filter to reconstruct  $i_C$  using  $v_C$  which is the accessible signal. Notice that such a proper filter is basically a time derivative operator with a limited bandwidth fixed by  $1/\sigma$ , which is also referred in control literature as "dirty" (or approximate) time derivative. The bandwidth is selected big enough to guarantee a good tracking of  $i_C$ . Since the higher order harmonics in  $i_C$  have been truncated in  $\hat{i}_C$ , due to the limited bandwidth of the estimator, then, also the higher order harmonics of  $i_m$  should be eliminated before computation of  $\hat{i}_L$  in (3.17) to avoid unnecessary distortion. The estimate of  $i_L$  can now be used in a surveillance block to guarantee a safer operation of the inverter system.

**Remark 3.6.1** It is clear that a much smaller  $\beta$  compared to  $\alpha$  would produce a faster response, as  $i_m$  is dominated mainly by  $i_c$ , however, it was observed from (3.17) that extremely low values of  $\beta$  makes the above estimator very sensitive to variations on parameter C. Thus, values for parameters  $\alpha$  and  $\beta$  should be carefully selected to establish a tradeoff between speed response and sensitivity.

## 4. PHYSICAL IMPLEMENTATION

## 4.1 Introduction

A N UPS prototype has been built to experimentally prove the proposed controller and estimator developed in Chapter 3. The power stage of the UPS system is built using a VSI produced by SEMIKRON under the commercial name "Power Electronics Teaching System". To eliminate the switching effect of the devices a smoothing LC filter is connected at the output of the VSI. A three phase diode rectifier feeding a resistor, plus a resistor connected in between two phases to produce unbalance are used as the distorted unbalanced load. The load is connected and disconnected from the UPS by means of a set of relays controlled from the computer.

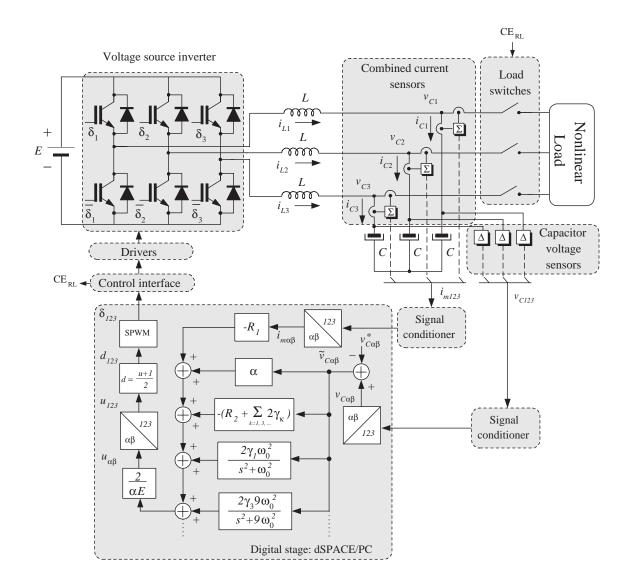

For the instrumentation of the inverter prototype we have introduced sensors, signal conditioners, voltage limiters and a control interface. The proposed controller and estimator have been implemented in a digital signal processor (DSP) based card ACE1103 made by dSPACE. This same card also performs the analog-to-digital (AD) conversion. The UPS system, the instrumentation stages and the proposed control are shown in Fig. 4.1.

The sensors and corresponding signal conditioners have been placed in the same card and communicated to the dSPACE card via a set of voltage limiters to protect the acquisition ports of the dSPACE. The sensed signals are the combined currents  $i_{m123}$  and the capacitor voltages  $v_{C123}$ . The used sensors provide galvanic isolation. The controller has been programmed using the environment Simulink/MATLAB, and then compiled and downloaded to the dSPACE card using the Realtime-Workshop tools included in Simulink package. The principal steps are described next: First, the sensed signals are transformed from 123-coordinates to  $\alpha\beta$ -coordinates, which are the feedback signals used in the proposed controller. Once the control signal u is computed, it is transformed from  $\alpha\beta$ -coordinates to 123-coordinates. This control signal is then mapped back to the duty cycle  $d_{123}$ , which is then injected in the SPWM to generate the switching sequence  $\delta_{123}$ .

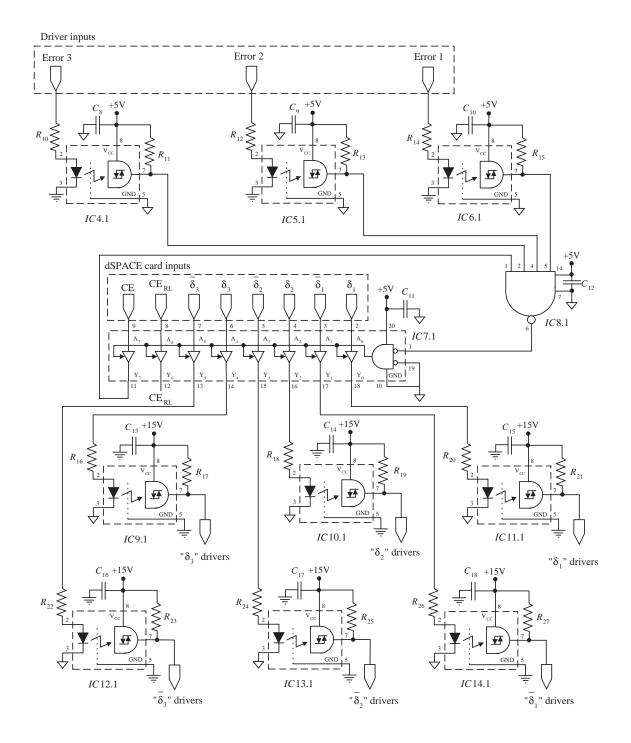

The control interface card communicates digital signals between the control stage, i.e., the dSPACE card, and the drivers feeding the gates of the power devices in the VSI. This card provides galvanic insolation between the dSPACE card and the drivers. The control interface is able to interrupt the SPWM switching sequence, if over current or over voltage conditions appear.

## 4.2 Power stages

### 4.2.1 Three-phase three-wire UPS system

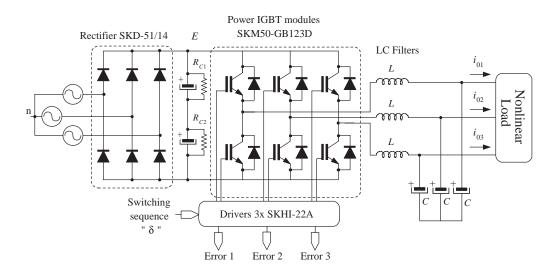

The "Power Electronics Teaching System" from SEMIKRON includes a three-phase diode rectifier SKD-51/14, a pair of capacitors of 2200  $\mu$ F, three drivers SKHI-22A and three half-bridge modules SKM50-GB123D implemented with IGBT and free-wheeling diode.

Figure 4.2 shows the implemented electric diagram for this stage. The input voltage E has been obtained using the rectifier SKD-51/14 and the pair of capacitors of 2200  $\mu$ F are connected in series. The driver SKHI-22A protects the IGBTs against short circuit and low power supply voltage. Each of the drivers SKHI-22A controls an inverter leg and provides an error signal (Error 1, Error 2 and Error 3) of negative logic, i.e., it gives a 15 V signal when there is no error. If an error condition is detected, the driver stops and the input impulses are ignored. The resetting of the error latch is achieved by forcing both inputs to zero, and suppressing the cause of the error. The drivers are independent from each other, therefore it is necessary to take

Fig. 4.1: General scheme of the UPS system with proposed control and instrumentation stages.

Fig. 4.2: Three-phase three-wire UPS system.

all the precautions to shut the system off when an error condition is sensed. All these precautions have been considered in the control interface card, which is described below. Each module SKM50-GB123D represents an inverter leg made of two IGBT, with antiparallel diode, connected in series. The IGBTs turned on, i.e., they conduct, if a 15 V signal is placed between gate and emitter, and they are turned off if a -15 V signal is placed instead. These control signals are delivered by the SKHI-22A, through an additional gate resistor of 30  $\Omega$ . Finally, the cut-off frequency of the output LC filter has been placed at approximately 1Khz, that is, a decade below the switching frequency. The parameters used in the UPS prototype system are collected in Table 4.1.

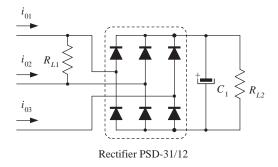

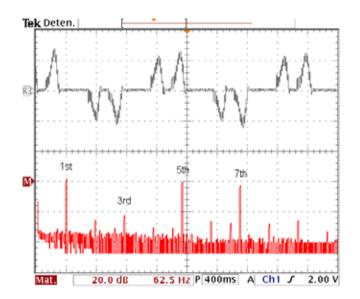

#### 4.2.2 Distorted unbalanced load

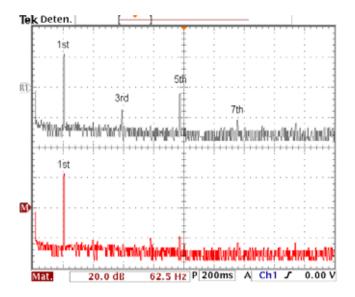

The nonlinear load is composed of a three-phase diode rectifier PSD-31/12 connected to a DC capacitor of 235  $\mu$ F feeding a resistor of 100  $\Omega$ . To produce the unbalance condition a resistor of 150  $\Omega$  is connected in between two phases. Figure 4.3 shows the implemented electrical circuit for the unbalanced nonlinear load. The elements used in the distorted unbalanced load are collected in Table 4.1. Figure 4.4 shows (top plot) the time response for one of the measured load currents, and (bottom plot) its corresponding frequency spectrum. Notice that the load current is composed mainly by odd harmonics of the fundamental  $f_0$ , mainly 1st, 3rd, 5th and 7th components. These harmonics are precisely the components considered for compensation, that is, the bank of resonant filters includes filters tuned at 1st, 3rd, 5th and 7th harmonic of the fundamental  $f_0$ .

Fig. 4.3: Distorted unbalanced load.

Fig. 4.4: Load current (only one phase): (top) the current signal i<sub>01</sub> in the time domain (x-axis 200 ms/div, y-axis 5 A/div) and (bottom) its corresponding frequency spectrum (x-axis 62.5 Hz/div, y-axis 20 dB/div).

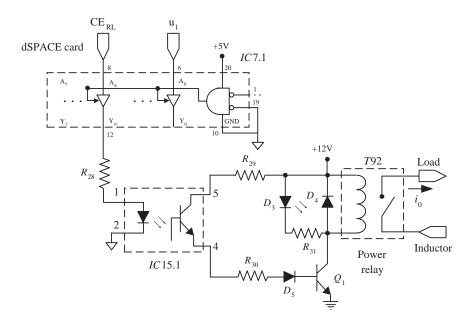

#### 4.2.3 Load switches

In the experimental results, it is necessary to obtain the transient response during the connection and disconnection of the load. This task is performed via a set of three relay switches, one for each phase, controlled from the computer. Figure 4.5 shows the implemented electrical circuit for the relay switches and their corresponding drivers. The buffer IC7.1 reinforces the  $CE_{RL}$  signal (this buffer is the same integrated circuit used in the control interface). The optocoupler IC15.1 provides galvanic insolation between the buffer and the inductor of the power relay T92. The resistances  $R_{29}$  and  $R_{30}$  limits the current across from the transistor of IC15.1. The diode  $D_5$  permits the current to flow only on the direction towards the transistor  $Q_1$ . The diode  $D_4$  deviates the inverse current produced by the bobbin of the power relay during the turn off. The light emitter diode  $D_3$  indicates the actual state of the power relay. Notice that, if the dSPACE control signal is the logic OFF, the transistor of the IC15.1 and the transistor  $Q_1$  do not conduct, while if it is ON, both transistors conduct activating the bobbin of the power relay allowing the output current to flow. The devices used in the relay based load switches are collected in Table 4.1.

Fig. 4.5: Electric circuit of the load switches.

| L                          | : | 1mH                    |

|----------------------------|---|------------------------|

| C                          | : | $25\mu\mathrm{F}$      |

| $C_1$                      | : | $235 \mu F$            |

| $R_{L1}$                   | : | $150\Omega$            |

| $R_{L2}$                   | : | $100\Omega$            |

| $R_{C1}, R_{C2}$           | : | $22\mathrm{k}\Omega$   |

| $R_{28}$                   | : | $330\Omega$            |

| $R_{29}, R_{31}$           | : | $2.2 \mathrm{k}\Omega$ |

| $R_{30}$                   | : | $220\Omega$            |

| $D_4, D_5$                 | : | 1N4937                 |

| $Q_1$                      | : | BC548                  |

| IC15.1                     | : | CNY17-2                |

| IGBTs                      | : | SKM50-GB123D           |

| Light emitter diode        | : | $D_3$                  |

| Power relay                | : | T92                    |

| Rectifier of input voltage | : | SKD-51/14              |

| Rectifier of load          | : | PSD-31/12              |

| Drivers                    | : | SKHI-22A               |

| Drivers                    | : | SKHI-22A               |

Table 4.1: Devices and parameters of the power stages.

## 4.3 Sensors and signal conditioning stages

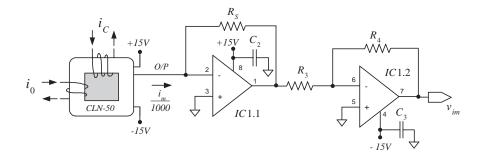

### 4.3.1 Combined current sensor arrangement

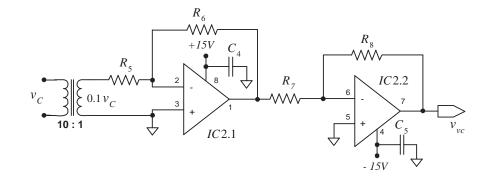

As it was mentioned, the proposed controller as well as the proposed observer have been implemented with the dSPACE card. Therefore, the combined current sensor should provide isolation between the power stage and the dSPACE based controller card. Moreover, it is necessary to limit such signals (one for each phase) to the admissible range [-10V, 10V] prior to send them to the analogical digital ports (ADP) of the dSPACE. Figure 4.6 shows the implemented electric circuit for the mixed current sensor. The mixed current is sensed with the current sensor CLN-50. This sensor provides electric isolation between the current carrying conductor(s) and the control circuit. The sensor CLN-50 is a closed-loop Hall effect current sensor that accurately measures DC and AC currents. In the CLN-50 both conductors, the one conducting the capacitor current and the other conducting the load current, have been wired as to obtain  $\alpha = 10$  and  $\beta = 1$ , that is, we have given 10 turns of the former and 1 turn for the latter. The sensor thus, furnishes directly the weighted sum of both currents. The operational amplifier IC1.1 is connected as *current-to-voltage converter*, i.e., the IC1.1 provides a proportional voltage to the mixed current. The IC2.1 regains the sign of the mixed current. The transfer function of the delivered voltage  $v_{im}$  is given by expression (4.1). The devices and parameters used in the combined current sensor circuit are collected in Table 4.2. Figure 4.7 shows a picture of the implemented cards.

Fig. 4.6: Electric circuit of the combined current sensor.

$$v_{im} = 1 \times 10^{-3} \frac{R_4}{R_3} R_S i_m \tag{4.1}$$

#### 4.3.2 Capacitor voltage sensor

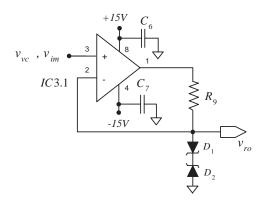

In the same form as in the combined current sensor, the capacitor voltage sensor should provide galvanic isolation between the power stage and the control circuit. Moreover, these capacitor voltage signals (one for each phase) should be limited prior to send them to the analogical digital converters (ADCs) in the dSPACE card. Figure 4.8 shows the implemented electric circuit for this stage. The transformer gives galvanic isolation between the capacitor voltage and the control stage. It also reduces

Fig. 4.7: Electric circuit of the combined current sensor.

| $R_S$          | : | $50\Omega$            |

|----------------|---|-----------------------|

| $R_3$          | : | $5\mathrm{k}\Omega$   |

| $R_4$          | : | $10 \mathrm{k}\Omega$ |

| $C_2, C_3$     | : | $0.1 \mu F$           |

| IC1.1, IC1.2   | : | TL082                 |

| Current sensor | : | CLN-50                |

|                |   |                       |

Table 4.2: Devices and parameters of the combined current sensor.