## INSTITUTO POTOSINO DE INVESTIGACIÓN CIENTÍFICA Y TECNOLÓGICA, A.C.

## POSGRADO EN CIENCIAS APLICADAS

## On modeling and control of Multilevel Converters and PLL algorithms

Tesis que presenta

Misael Francisco Martínez Montejano

Para obtener el grado de

### **Doctor en Ciencias Aplicadas**

En la opción de

**Control y Sistemas Dinámicos**

Director de la Tesis: Dr. Gerardo Escobar Valderrama

San Luis Potosí, S.L.P., junio de 2009.

### Constancia de aprobación de la tesis

La tesis "On modeling and control of Multilevel Converters and PLL algorithms" presentada para obtener el Grado de de Doctor(a) en Ciencias Aplicadas en la opción de Control y Sistemas Dinámicos fue elaborada por Misael Francisco Martinez Montejano y aprobada el 5 de junio de 2009 por los suscritos, designados por el Colegio de Profesores de la División de Matemáticas Aplicadas del Instituto Potosino de Investigación Científica y Tecnológica, A.C.

Dr. Gerardo Escobar Valderrama Director de Tesis

Dr. Nimrod Vázquez Nava Ásesor de Tesis

Dr. Jain eĺ sesor de Tesis

Dra. Hse Cervantes Camacho Asesora de Tesis

Dr. Arturo Zavala Rio Asesor de Tesis

ij

### **Créditos Institucionales**

Esta tesis fue elaborada en el Laboratorio de Procesamiento y Calidad de la Energía de la División de Matemáticas Aplicadas del Instituto Potosino de Investigación Científica y Tecnológica, A.C., bajo la dirección del Dr. Gerardo Escobar Valderrama.

Durante la realización del trabajo el autor recibió una beca académica del Consejo Nacional de Ciencia y Tecnología con número de registro 172379 y del Instituto Potosino de Investigación Científica y Tecnológica, A. C.

# Instituto Potosino de Investigación Científica y Tecnológica, A.C.

## Acta de Examen de Grado

El Secretario Académico del Instituto Potosino de Investigación Científica y Tecnológica, A.C., certifica que en el Acta 007 del Libro Primero de Actas de Exámenes de Grado del Programa de Doctorado en Ciencias Aplicadas en la opción de Control y Sistemas Dinámicos está asentado lo siguiente:

En la ciudad de San Luis Potosí a los 5 días del mes de junio del año 2009, se reunió a las 10:00 horas en las instalaciones del Instituto Potosino de Investigación Científica y Tecnológica, A.C., el Jurado integrado por:

| Dr. Jaime Eugenio Arau Roffiel | Presidente | CENIDET |

|--------------------------------|------------|---------|

| Dr. Gerardo Escobar Valderrama | Secretario | IPICYT  |

| Dr. Arturo Zavala Río          | Sinodal    | IPICYT  |

| Dra. Ilse Cervantes Camacho    | Sinodal    | IPICYT  |

| Dr. Arturo Zavala Río          | Sinodal    | IPICY   |

a fin de efectuar el examen, que para obtener el Grado de:

DOCTOR EN CIENCIAS APLICADAS EN LA OPCIÓN DE CONTROL Y SISTEMAS DINÁMICOS

sustentó el C.

Misael Francisco Martínez Montejano

sobre la Tesis intitulada:

#### On modeling and control of multilevel converters and PLL algorithms

que se desarrolló bajo la dirección de

#### Dr. Gerardo Escobar Valderrama

El Jurado, después de deliberar, determinó

#### **APROBARLO**

Dándose por terminado el acto a las 12:42 horas, procediendo a la firma del Acta los integrantes del Jurado. Dando fe el Secretario Académico del Instituto.

A petición del interesado y para los fines que al mismo convengan, se extiende el presente documento en la ciudad de San Luis Potosí, S.L.P., México, a los 5 días del mes de junio de 2009.

Dr. Narcial Bonilla Marín Secretario Académico 8 INSTITUTO POTOSINO DE INVESTIGACIÓN DE INVESTIGACIÓN DIENTÍFICA Y TECNOLÓGICA, A.C. IPICYT SECRETARIA ACADEMICA Mtra. Ivonne Lizette Chevas Velez Jefa del Departamento de Asuntos Escolares

# On modeling and control of multilevel converters and PLL algorithms

M.Sc. Misael Francisco Martínez Montejano

June 2009

To my parents with love

# Summary

The present thesis is focuses in the study of the multilevel converters and the phaselocked loop algorithms.

In the first five chapters, two of the main topologies of multilevel converters are studied, namely, diode clamped multilevel converter (NPC) and cascaded H-bridge multilevel converter (HB). First, a model is obtained that described the dynamics of the three level NPC converter used in a synchronous rectifier application. The highly nonlinear model, originally in *abc*-coordinates, is also expressed in its  $\alpha\beta\gamma$ -coordinates. Special attention is given to the  $\gamma$ -component of the control input, which represents a degree of freedom crucial for the balancing of the capacitors voltages. Then, based on this model, it is presented an adaptive controller that guarantees regulation and balance of the output capacitors voltages, as well as a close to unity power factor. Next, the modeling and the control design processes are presented for a cascade H-bridge single-phase multilevel converter used as a shunt active filter. Crucial for the developments is the transformation of the model in terms of the sum and the difference of the squares of the capacitors voltages. Moreover, it is shown that, while the current tracking problem and the regulation problem depend on the sum of the injected voltages, the balance depends on the difference between them. It is also presented a controller for the cascade H-bridge three-phase multilevel converter used as a shunt active filter. Based on the proposed mathematical model, the controller is designed to compensate harmonic distortion and reactive power due to a nonlinear distorting load. Simultaneously, the controller guarantees regulation and balance of all capacitor voltages. The idea behind the controller is to allow distortion of the current reference during the transients to guarantee regulation and balance of the capacitors voltages.

The chapters 6 and 7 of the thesis deals with the design of phase-locked loop (PLL) algorithms. Although PLLs have been widely used in many electronic applications, the PLL presented here is of special interest in the synchronization of power electronic equipment coupled with the electric network. In particular, the presented PLL has been designed to work in fixed reference frame coordinates, and thus the proposed algorithm is referred as fixed reference frame PLL (FRF-PLL). The scheme provides an estimation of the angular frequency, and both the positive and negative sequences of the fundamental component of a three-phase signal. The design of the FRF-PLL is based on a complete description of the source voltage involving both positive and negative sequences in stationary coordinates and considering that the angular frequency is uncertain. Therefore the proposed scheme is of special interest in cases of unbalanced operation. Also, a simpler scheme is presented for the balanced case. Finally, the design and implementation of a single-phase PLL based on an adaptive observer is also presented. This algorithm assumes that the signal is produced by a harmonic oscillator where the frequency is an unknown parameter, and only one of the

states is available. In contrast to many PLL schemes, the proposed scheme does not rely in the usual assumption of linearity around the desired equilibrium point, which leads to local results.

# Contents

|   | Not                             | ation                                                                                                                                                                                                                                                                                                                     | xi                                                              |

|---|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|   | List                            | t of figures                                                                                                                                                                                                                                                                                                              | xiii                                                            |

| 1 | 1.1<br>1.2                      | oduction         Topologies of multilevel converters         Classification of Modulation Strategies                                                                                                                                                                                                                      | <b>19</b><br>22<br>25                                           |

|   | 1.3<br>1.4                      | Phase locked-loop algorithmsObjectives, structure and main contributions                                                                                                                                                                                                                                                  | 26<br>27                                                        |

| 2 | NPC<br>2.1<br>2.2<br>2.3<br>2.4 | C Multilevel Converter: Mathematical Model         Introduction          Model of the three level NPC inverter          2.2.1       The inductors current dynamics         2.2.2       The capacitors voltages dynamics         2.2.3       Transformation to $\alpha\beta\gamma$ -coordinates         Model verification | <b>31</b><br>31<br>32<br>33<br>35<br>39<br>42<br>43             |

| 3 |                                 | C Multilevel Converter: Adaptive Controller for a Three-level Synchronous tifier         Introduction                                                                                                                                                                                                                     | <b>45</b><br>45<br>45<br>46<br>47<br>48<br>49<br>50<br>54<br>58 |

| _ | 3.6                             | Conclusions                                                                                                                                                                                                                                                                                                               | 58                                                              |

| 4 | Mod<br>4.1<br>4.2<br>4.3        | Ieling and Control of a Single-phase Cascade H-Bridge Multilevel Converter         Introduction          Model of the five level HB multilevel converter          Controller design                                                                                                                                       | • <b>63</b><br>63<br>64<br>66                                   |

|   |                   | 4.3.1 Current tracking loop                                                         | 66                |

|---|-------------------|-------------------------------------------------------------------------------------|-------------------|

|   |                   | 4.3.2 Regulation loop                                                               | 67                |

|   |                   | 4.3.3 Balance loop                                                                  | 68                |

|   | 4.4               | Numerical results                                                                   | 68                |

|   | 4.5               | Some preliminary experimental results                                               | 71                |

|   | 4.6               | Conclusions                                                                         | 71                |

| - | Л                 |                                                                                     |                   |

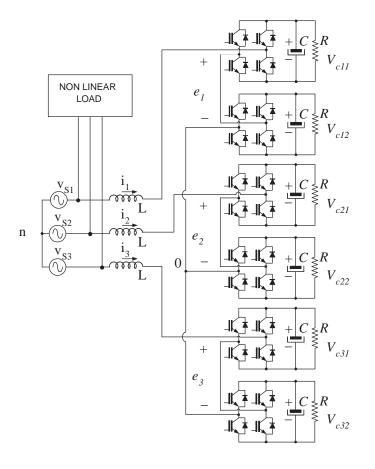

| 5 |                   | leling and Control of a Three-phase Five-level Cascade H-Bridge Multileve<br>verter | I<br>75           |

|   | 5.1               | Introduction                                                                        | 75                |

|   | 5.2               | System description                                                                  | 76                |

|   | 5.2               | Model transformation                                                                | 78                |

|   | 5.5               | 5.3.1 Main assumptions                                                              | 80                |

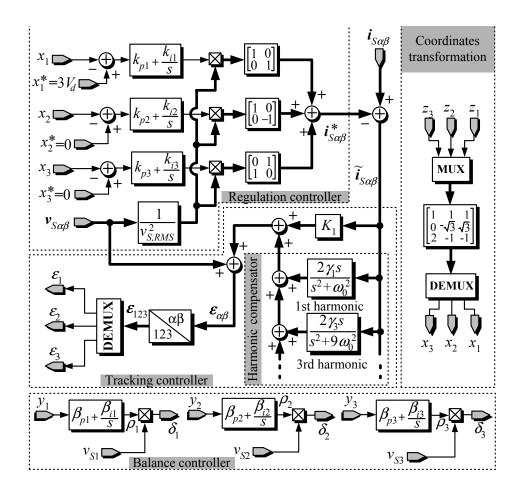

|   | 5.4               | Control design                                                                      | 81                |

|   | Э.т               | 5.4.1 Current tracking loop                                                         | 82                |

|   |                   | 5.4.2 Regulation loop                                                               | 82                |

|   |                   | 5.4.2       Kegulation loop         5.4.3       Voltage balance loop                | 83                |

|   |                   | 5.4.4 Design criteria for the controller parameters                                 | 84                |

|   | 5.5               | Numerical results                                                                   | 87                |

|   | 5.6               | Conclusions                                                                         | 87                |

|   | 5.0               |                                                                                     | 07                |

| 6 | A Pl              | hase-Locked-Loop based on an adaptive observer                                      | 91                |

|   | 6.1               | Introduction                                                                        | 91                |

|   | 6.2               | Model of the single phase grid voltage                                              | 92                |

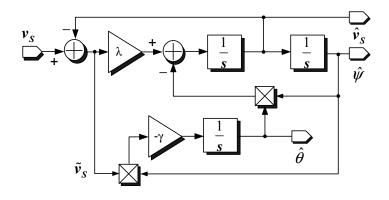

|   | 6.3               | Description of the proposed PLL                                                     | 92                |

|   |                   | 6.3.1 The single phase grid voltage estimator                                       | 92                |

|   |                   | 6.3.2 Estimation of the fundamental frequency                                       | 93                |

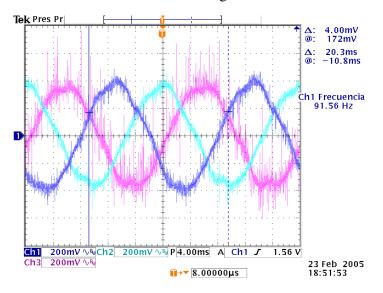

|   | 6.4               | Experimental results                                                                | 94                |

|   | 6.5               | Conclusions                                                                         | 94                |

| 7 | FRF               | -PLL                                                                                | 97                |

|   | 7.1               | Introduction                                                                        | 97                |

|   | 7.2               | Model of the grid voltage in unbalanced condition                                   | 98                |

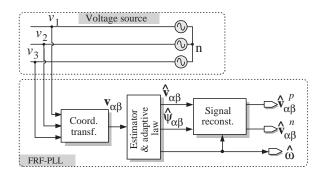

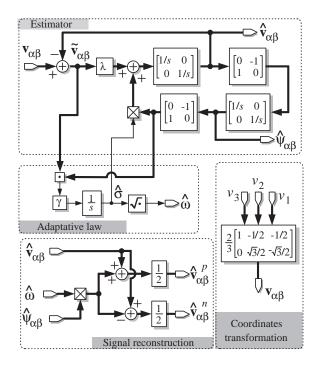

|   | 7.3               | Description of the proposed FRF-PLL                                                 | 100               |

|   |                   | 7.3.1 The grid voltage estimator                                                    | 100               |

|   |                   | 7.3.2 Estimation of the angular frequency                                           | 100               |

|   |                   | 7.3.3 Estimation of positive and negative sequences of the grid voltage             | 101               |

|   | 7.4               | Tuning of the FRF-PLL algorithm                                                     | 101               |

|   | 7.5               | Numerical results                                                                   | 103               |

|   | 7.6               | Experimental results                                                                | 104               |

|   | 7.7               | Conclusions                                                                         | 111               |

| 0 | C                 |                                                                                     | 112               |

| 8 | <b>Con</b><br>8.1 | clusions, future research and scientific production                                 | <b>113</b><br>115 |

|   | 0.1               |                                                                                     | 113               |

### Bibliography

119

# Notation

### **Frequent Acronyms**

| AC     | alternating current.                                    |

|--------|---------------------------------------------------------|

| BIBO   | bounded input bounded output.                           |

| BBD    | bucket brigade delay.                                   |

| DC     | direct current.                                         |

| DC-DC  | direct current to direct current.                       |

| EMI    | electro magnetic interference.                          |

| DSP    | digital signal processor.                               |

| ESR    | equivalent series resistances.                          |

| FFT    | fast Fourier transform.                                 |

| HR     | harmonic reducer.                                       |

| IC     | integrated circuit.                                     |

| IGBT   | isolated gate bipolar transistor.                       |

| LPF    | low pass filter.                                        |

| LTI    | linear time invariant.                                  |

| MOSFET | metal-oxide-semiconductor field-effect transistor.      |

| PCC    | point of common connection.                             |

| PF     | power factor.                                           |

| PFC    | power factor correctors or unit power factor converter. |

| PI     | proportional integral.                                  |

| PIS    | synchronous proportional integral.                      |

| PWM    | pulse width modulation.                                 |

| SPWM   | sine pulse width modulation.                            |

| RHS    | right hand side.                                        |

| RMS    | root mean square.                                       |

| THD    | total harmonic distortion.                              |

|        |                                                         |

| VSI    | voltage source inverter.                                |

| Most common mathematical symbols                                      |                                                                                         |  |  |  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|

| R                                                                     | field of real numbers.                                                                  |  |  |  |

| $\mathbb{C}$                                                          | field of complex numbers.                                                               |  |  |  |

| $\mathbb{R}^{m \times n}_{-}$ or $\mathbb{R}_{-}$                     | set of all proper and real rational stable transfer matrices.                           |  |  |  |

| $\mathbb{R}^n$                                                        | linear space of ordered $n$ -tuples in $\mathbb{R}$ .                                   |  |  |  |

| $\in$                                                                 | "belong to".                                                                            |  |  |  |

| $\stackrel{\triangle}{=}$                                             | "defined as".                                                                           |  |  |  |

| $(\cdot)^	op$ $(\cdot)^{-1}$                                          | transpose operator.                                                                     |  |  |  |

| $(\cdot)^{-1}$                                                        | inverse operator.                                                                       |  |  |  |

| $\bar{\sigma}(.)$                                                     | largest singular value of the matrix.                                                   |  |  |  |

| $\frac{Re(\alpha)}{\mathscr{L}^{-1}}$                                 | the real part of $\alpha \in \mathbb{C}$ .                                              |  |  |  |

| $\mathscr{L}^{-1}$                                                    | inverse Laplace transform.                                                              |  |  |  |

| $\left\ A ight\ _{\infty} \mathcal{L}_2$                              | induced $\infty$ -norm of a matrix A.                                                   |  |  |  |

| $\mathcal{L}_2$                                                       | space of square integrable functions.                                                   |  |  |  |

| $\mathcal{L}_\infty$                                                  | space of bounded functions.                                                             |  |  |  |

| $\mathcal{H}_\infty$                                                  | set of $\mathcal{L}_{\infty}$ analytic in $Re(s) > 0$ .                                 |  |  |  |

| prefix $\mathcal{R}$                                                  | real rational, e.g., $\mathcal{RH}_{\infty}, \mathcal{RH}_{\in}$ .                      |  |  |  |

| t .                                                                   | time, $t \in \mathbb{R}_{\geq 0}$ .                                                     |  |  |  |

| $ \frac{\frac{d}{dt}(\cdot), (\cdot)}{(\cdot)_k^p}, $ $ (\cdot)_k^n $ | differentiation operator.                                                               |  |  |  |

| $(\cdot)_k^p$ ,                                                       | k-th harmonic coefficients for the positive sequence representation.                    |  |  |  |

| $(\cdot)_k^n$                                                         | k-th harmonic coefficients for the negative sequence representation.                    |  |  |  |

| $I_n$                                                                 | identity matrix of dimension n.                                                         |  |  |  |

| ${\mathcal J}$                                                        | skew symmetric matrix $\begin{bmatrix} 0 & -1 \\ 1 & 0 \end{bmatrix}$                   |  |  |  |

| $e^{(\cdot)}$                                                         | exponential function                                                                    |  |  |  |

| ${\cal H}$                                                            | set of indexes of the considered harmonic components                                    |  |  |  |

| $ ho(\cdot)$                                                          | rotation vector defined as $\begin{bmatrix} \cos(\cdot) \\ \sin(\cdot) \end{bmatrix}$ . |  |  |  |

| $ \begin{array}{c} \hat{(\cdot)} \\ \tilde{(\cdot)} \end{array} $     | estimate of $(\cdot)$ .                                                                 |  |  |  |

| $(\tilde{\cdot})$                                                     | error between a quantity and its reference.                                             |  |  |  |

|                                                                       | $(\cdot) - (\cdot)^*, (\hat{\cdot}) - (\cdot).$                                         |  |  |  |

| $(\cdot)^*$                                                           | desired external references.                                                            |  |  |  |

# **List of Figures**

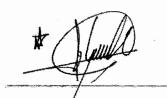

| 1.1 | Synthesis of the output voltage in multilevel converters: <b>a</b> ) two levels, <b>b</b> ) three levels and <b>c</b> ) n-levels.                                                                                                                                  | 21 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

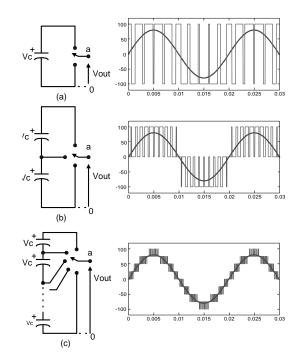

| 1.2 | Neutral Point Clamped (NPC) multilevel converter.                                                                                                                                                                                                                  | 23 |

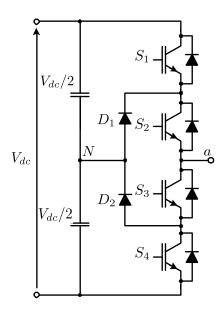

| 1.3 | Flying capacitor (FC) multilevel converter.                                                                                                                                                                                                                        | 24 |

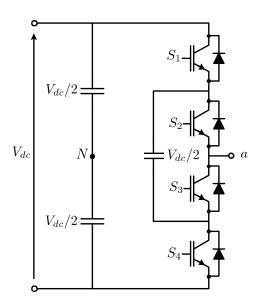

| 1.4 | H-bridge (HB) multilevel converter.                                                                                                                                                                                                                                | 24 |

| 2.1 | Synchronous rectifier based on a three level NPC inverter                                                                                                                                                                                                          | 32 |

| 2.2 | Synchronous rectifier equivalent circuit based on a three level inverter with ideal switches.                                                                                                                                                                      | 33 |

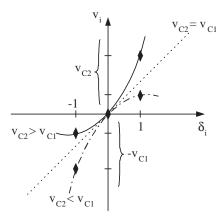

| 2.3 | Description of the voltages functions $v_i$ using a quadratic function of $\delta_i$ fitting<br>all three points ( $\blacklozenge$ ), valid for each $i \in \{1, 2, 3\}$ . For: (-) $v_{C_1} > v_{C_2}$ , ()<br>$v_{C_1} < v_{C_2}$ , and () $v_{C_1} = v_{C_2}$ . | 34 |

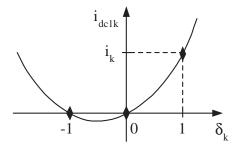

| 2.4 | Description of the current functions $i_{dc1k}$ using a quadratic function of $\delta_k$ ,                                                                                                                                                                         |    |

|     | fitting all three points ( $\blacklozenge$ ), valid for each $k \in \{1, 2, 3\}$ .                                                                                                                                                                                 | 36 |

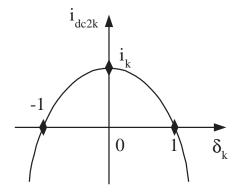

| 2.5 | Description of the current functions $i_{dc2k}$ using a quadratic function of $\delta_k$ , fitting all three points ( $\blacklozenge$ ), valid for each $k \in \{1, 2, 3\}$ .                                                                                      | 36 |

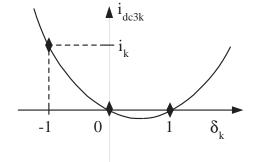

| 2.6 | Description of the current functions $i_{dc3k}$ using a quadratic function of $\delta_k$ , fitting all three points ( $\blacklozenge$ ), valid for each $k \in \{1, 2, 3\}$ .                                                                                      | 37 |

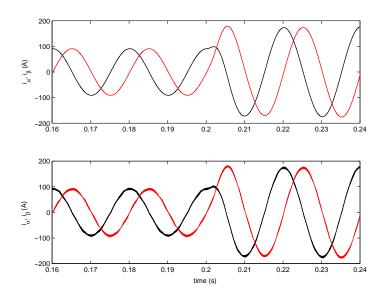

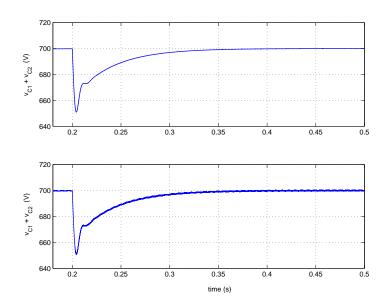

| 2.7 | Input currents $i_{\alpha\beta}$ responses to a load step change from $20\Omega$ to $10\Omega$ at $t = 0.2$ s: (Top) Proposed model and (Bottom) switching system driven by pulses.                                                                                | 43 |

| 2.8 | Sum of voltages $x_3 = v_{C1} + v_{C2}$ responses to a load step change from $20\Omega$ to $10\Omega$ at $t = 0.2$ s: ( <b>Top</b> ) Proposed model and ( <b>Bottom</b> ) switching system driven by pulses                                                        | 44 |

| 2.9 | Difference of voltages $x_4 = v_{C1} - v_{C2}$ responses to a load step change from $20\Omega$ to $10\Omega$ at $t = 0.2$ s: ( <b>Top</b> ) Proposed model and ( <b>Bottom</b> ) switching system driven by pulses                                                 | 44 |

| 3.1 | Block diagram of the overall controller including tracking, regulation and                                                                                                                                                                                         |    |

| 5.1 | balance control loops.                                                                                                                                                                                                                                             | 54 |

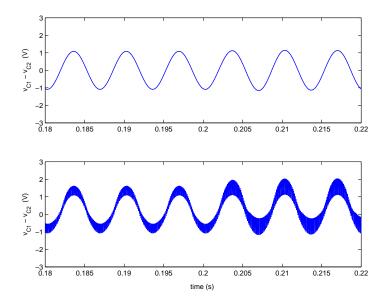

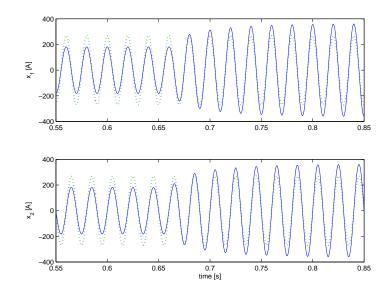

| 3.2 | Transient response of input currents to a load step change from $20 \Omega$ to $10 \Omega$<br>at $t = 0.66$ s: ( <b>Top</b> ) $x_1$ in solid and $v_{s1}$ in dotted line; ( <b>Bottom</b> ) $x_2$ in solid                                                         |    |

|     | and $v_{s2}$ in dotted line                                                                                                                                                                                                                                        | 56 |

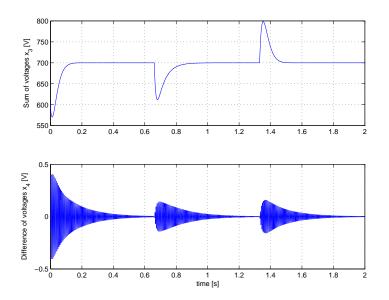

| 3.3        | Transient response, during a load resistor change from $20\Omega$ to $10\Omega$ at $t = 0.66$ s, and back to $20\Omega$ at $t = 1.33$ s, of: ( <b>Top</b> ) the sum of capacitors voltages                                                |     |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | $x_3 = v_{C1} + v_{C2}$ , and (Bottom) the difference of capacitors voltages $x_4 =$                                                                                                                                                      |     |

|            | $v_{C1} - v_{C2}$                                                                                                                                                                                                                         | 56  |

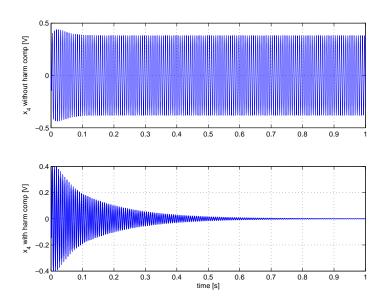

| 3.4        | Transient response of the difference of capacitors voltages $x_4 = v_{C1} - v_{C2}$<br>from start up: ( <b>Top</b> ) without harmonic compensation, and ( <b>Bottom</b> ) with                                                            |     |

|            | harmonic compensation.                                                                                                                                                                                                                    | 57  |

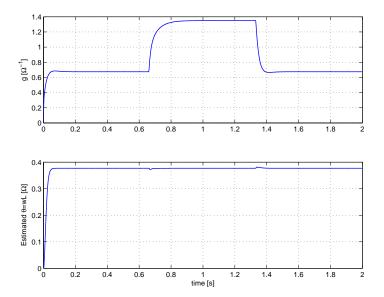

| 3.5        | Transient response, during a load resistor change from $20\Omega$ to $10\Omega$ at $t =$                                                                                                                                                  |     |

|            | 0.66s, and back to 20 $\Omega$ at $t = 1.33$ s, of: (Top) the gain g, and (Bottom) the                                                                                                                                                    |     |

|            | estimate $\hat{\theta} = \widehat{wL}$ .                                                                                                                                                                                                  | 57  |

| 3.6        | Compensated source currents $i_{S123}$                                                                                                                                                                                                    | 58  |

| 3.7        | Compensated source currents $i_{S123}$                                                                                                                                                                                                    | 59  |

| 3.8        | Capacitor voltages during a load change                                                                                                                                                                                                   | 59  |

| 3.9        | Rectified voltage during a load change from 1kW to 10kW (800V)                                                                                                                                                                            | 60  |

| 3.10       | Rectified voltage in a reference change from 750V to 850V                                                                                                                                                                                 | 60  |

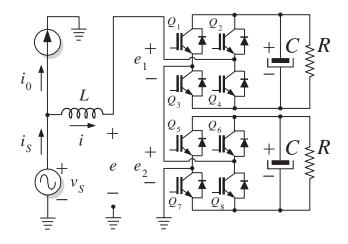

| 4.1        | Single-phase five-level cascade h-bridge converter used as a shunt active filter.                                                                                                                                                         | 64  |

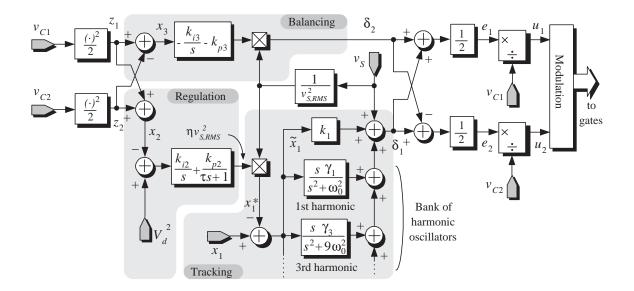

| 4.2        | Block diagram of the overall proposed controller.                                                                                                                                                                                         | 67  |

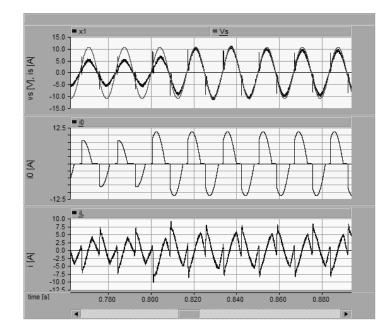

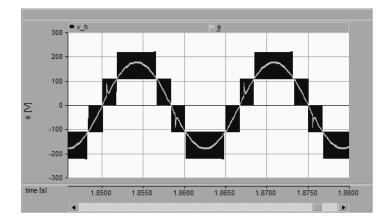

| 4.3        | (from top to bottom) Transient responses of line voltage $v_S(t)$ , compen-                                                                                                                                                               |     |

|            | sated current $i_S(t)$ , load current $i_0(t)$ , and injected current $i(t)$ during a load                                                                                                                                                |     |

|            | step change                                                                                                                                                                                                                               | 69  |

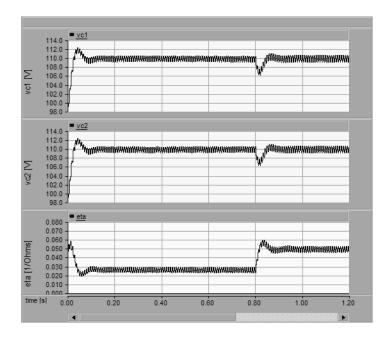

| 4.4        | (from top to bottom) Transient responses of the capacitor voltages $v_{C1}(t)$<br>and $v_{C2}(t)$ , and apparent conductance $\eta(t)$ observed by the source at start-up                                                                 |     |

|            | and during a load change                                                                                                                                                                                                                  | 70  |

| 4.5        | (gray) Injected voltage $e$ as computed in the control algorithm, and (black) the real injected voltage $e$ using a multicarrier phase-shifted modulation al-                                                                             |     |

|            | gorithm.                                                                                                                                                                                                                                  | 70  |

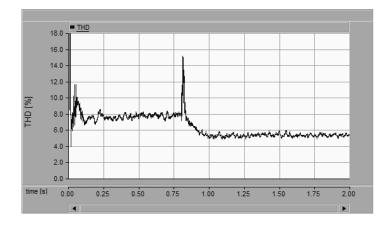

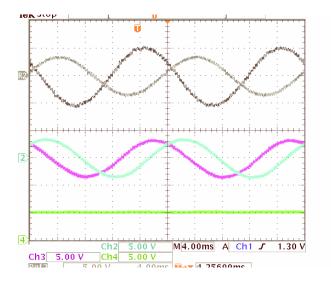

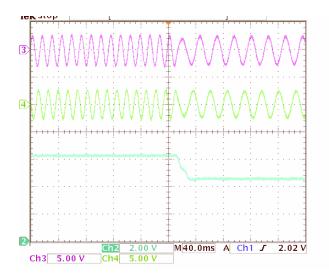

| 4.6<br>4.7 | THD of the compensated current $i_S$ at start-up and during a load change<br>Transient response observed during a start-up. The figure shows, from top to<br>bottom, both capacitor voltages, the converter output voltage and the source | 71  |

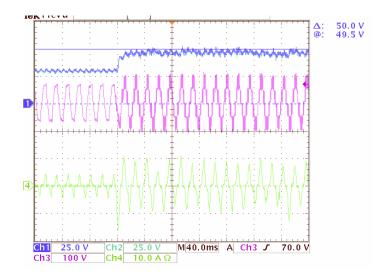

|            | current                                                                                                                                                                                                                                   | 72  |

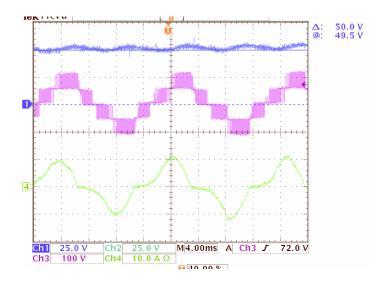

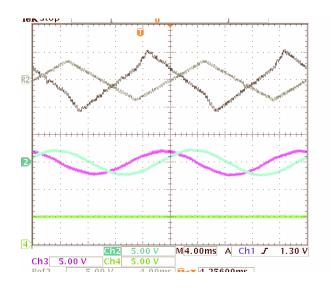

| 4.8        | From top to bottom, both capacitor voltages, the converter output voltage                                                                                                                                                                 |     |

|            | and the source current.                                                                                                                                                                                                                   | 72  |

| 4.9        | shows the capacitor voltages (TOP), the injected voltage and the source cur-                                                                                                                                                              | . – |

| ,          | rent in phase with the source voltage (in black).                                                                                                                                                                                         | 73  |

| 4.10       | From top to bottom, the capacitor voltages, the injected voltage $e$ as com-                                                                                                                                                              | 10  |

|            | puted in the control algorithm (in black) and the resulting modulated signal                                                                                                                                                              |     |

|            | using the multicarrier phase-shifted modulation algorithm, and the source                                                                                                                                                                 |     |

|            | current                                                                                                                                                                                                                                   | 73  |

| 5.1        | Three-phase five-level cascade H-bridge converter.                                                                                                                                                                                        | 76  |

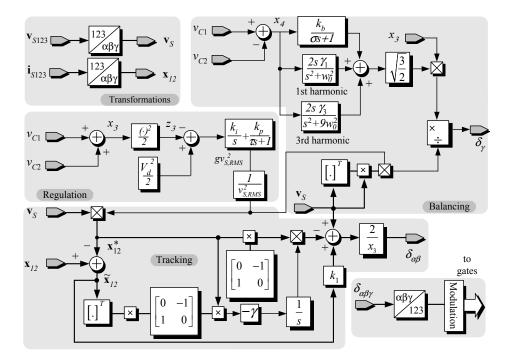

| 5.2        | Block diagram of the overall controller including tracking, regulation and                                                                                                                                                                |     |

|            | balance control loops.                                                                                                                                                                                                                    | 85  |

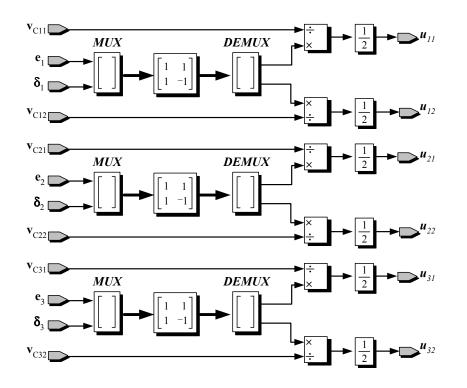

| 5.3        | Block diagrams of the controls combinations to generate the control inputs                                                                                                                                                                |     |

|            | in the original coordinates.                                                                                                                                                                                                              | 86  |

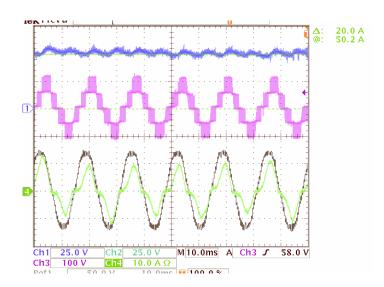

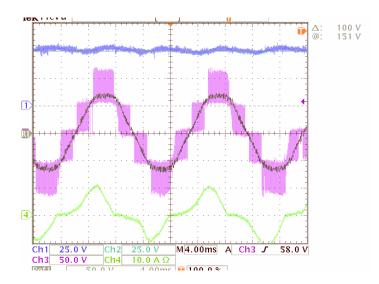

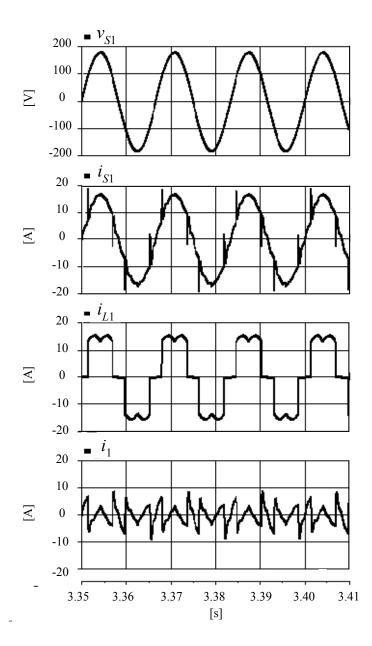

| 5.4<br>5.5 | Steady state response with the proposed solution of (from top to bottom):<br>line voltage $v_{S1}$ , line current $i_{S1}$ , load current $i_{01}$ , and injected current $i_1$<br>Transient response of the capacitors voltages during a load change                                                                                                                                                          | 88<br>89 |

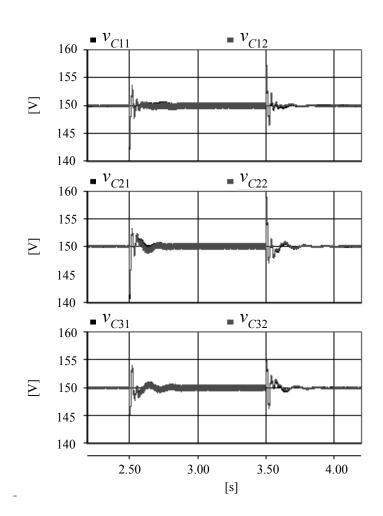

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

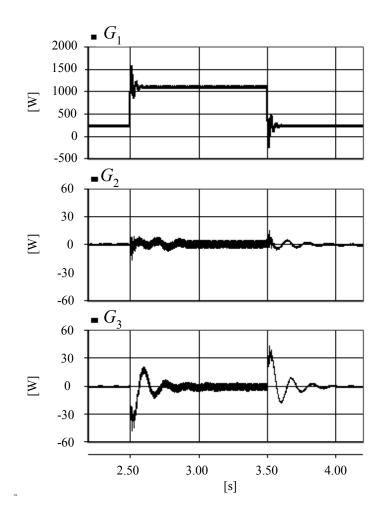

| 5.6<br>5.7 | Transient response of (from top to bottom): scaled apparent conductance $G_1 = g_1 v_{S,RMS}^2$ (dissipated power), and extra control inputs $G_2 = g_2 v_{S,RMS}^2$ and $G_3 = g_3 v_{S,RMS}^2$ during a load change                                                                                                                                                                                          | 90<br>90 |

| 6.1        | Block diagram of the proposed PLL algorithm.                                                                                                                                                                                                                                                                                                                                                                   | 93       |

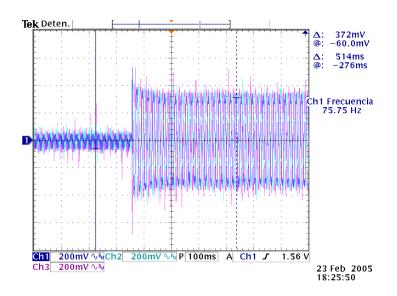

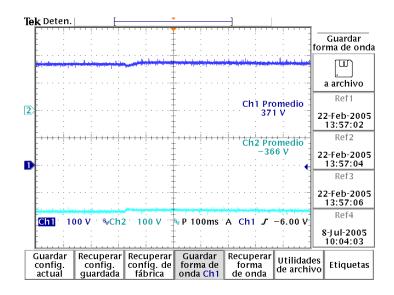

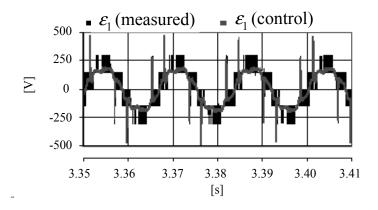

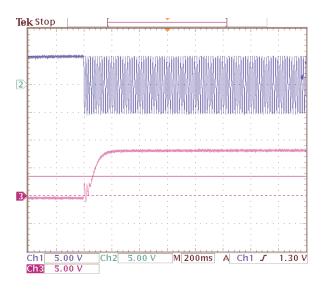

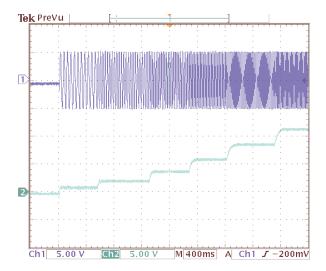

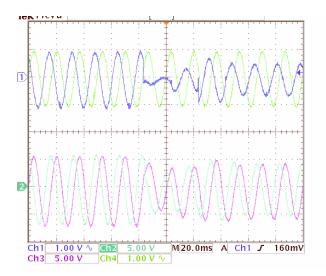

| 6.2        | Response of the proposed PLL scheme (top) estimated $\hat{v}_S$ and (bottom) es-                                                                                                                                                                                                                                                                                                                               |          |

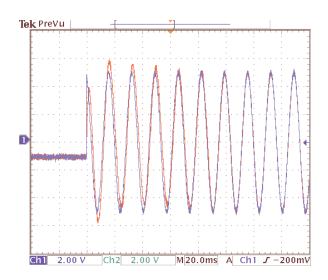

| (2)        | timated $\hat{\theta}$ .                                                                                                                                                                                                                                                                                                                                                                                       | 94<br>05 |

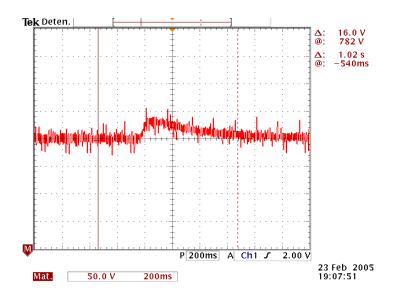

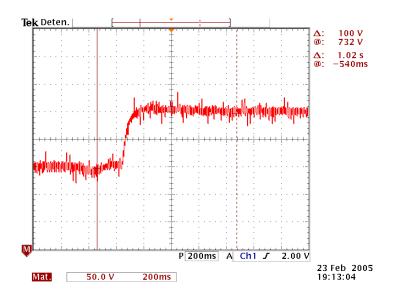

| 6.3<br>6.4 | Zoom of the transient response of the estimated $\hat{v}_S$ and measured $v_S$<br>Response of the proposed PLL when the utility frequency is changed in steps                                                                                                                                                                                                                                                  | 95       |

| ( 5        | from 20 to 120 Hz. (top) Utility voltage $v_S$ , and (bottom) estimated $\theta$                                                                                                                                                                                                                                                                                                                               | 95<br>06 |

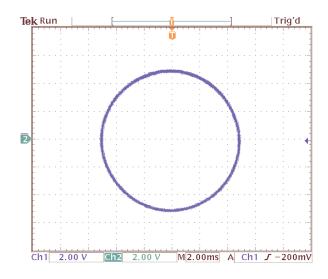

| 6.5        | Depicts the XY plot of estimated $\hat{v}_S$ versus estimated $\hat{\psi}$                                                                                                                                                                                                                                                                                                                                     | 96       |

| 7.1        | Connection of the proposed FRF-PLL to the electric utility                                                                                                                                                                                                                                                                                                                                                     | 101      |

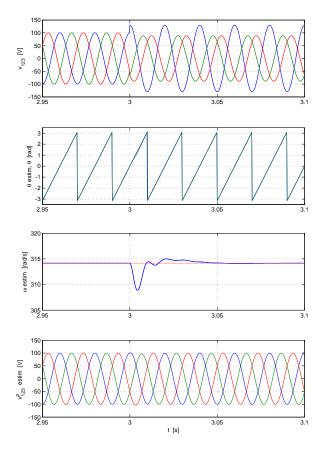

| 7.2<br>7.3 | Block diagram of the proposed FRF-PLL algorithm Depicts the transient response of the proposed FRF-PLL when the utility voltage goes from a balanced to an unbalanced condition. (from top to bottom) Utility voltage $v_{123}$ , estimated phase angle $\hat{\theta}$ , estimated angular frequency $\hat{\omega}$ , and estimated positive-sequence voltage in the synchronous reference frame $v_{123}^{p}$ | 102      |

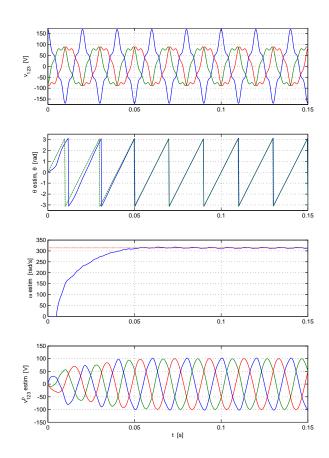

| 7.4        | Depicts the response of the proposed FRF-PLL to an unbalanced distorted utility voltage during start-up. (from top to bottom) Utility voltage $v_{123}$ , estimated phase angle $\hat{\theta}$ , estimated angular frequency $\hat{\omega}$ , and estimated positive-sequence voltage in the synchronous reference frame $v_{123}^{p}$                                                                         | 105      |

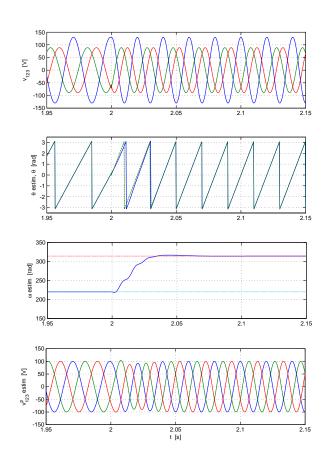

| 7.5        | Depicts the transient response of the proposed FRF-PLL to a utility fre-<br>quency change from 50 Hz to 35 Hz. (from top to bottom) Utility voltage $v_{123}$ , estimated phase angle $\hat{\theta}$ , estimated angular frequency $\hat{\omega}$ , and estimated<br>positive-sequence voltage in the synchronous reference frame $\hat{v}_{123}^p$                                                            | 106      |

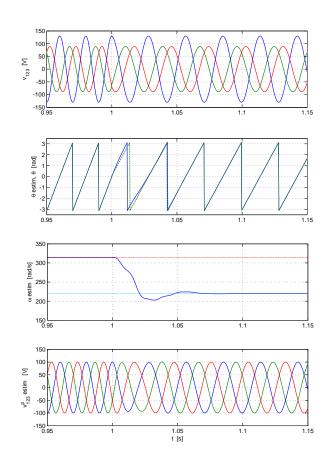

| 7.6        | Depicts the transient response of the proposed FRF-PLL to a utility fre-<br>quency change from 35 Hz to 50 Hz. (from top to bottom) Utility voltage $v_{123}$ , estimated phase angle $\hat{\theta}$ , estimated angular frequency $\hat{\omega}$ , and estimated                                                                                                                                              |          |

| 7.7        | positive-sequence voltage in the synchronous reference frame $\hat{v}_{123}^p$<br>Depicts the response of the proposed FRF-PLL when the utility voltage has<br>an unbalanced condition. (from top to bottom) Utility voltage $v_{\alpha\beta}$ , estimated<br>positive-sequence voltage in the fixed reference frame $\hat{v}_{\alpha\beta}^p$ and estimated an-                                               | 107      |

| 7.8        | gular frequency $\hat{\omega}$<br>Depicts the response of the proposed FRF-PLL to an unbalanced highly dis-<br>torted utility voltage. (from top to bottom) Utility voltage $v_{\alpha\beta}$ , estimated<br>positive-sequence voltage in the fixed reference frame $\hat{v}^p_{\alpha\beta}$ and estimated an-                                                                                                | 108      |

|            | gular frequency $\hat{\omega}$                                                                                                                                                                                                                                                                                                                                                                                 | 109      |

| 7.9  | Depicts the transient response of the proposed FRF-PLL when the utility                      |     |  |  |

|------|----------------------------------------------------------------------------------------------|-----|--|--|

|      | voltage goes from a balanced to an unbalanced condition. (top) Utility volt-                 |     |  |  |

|      | age $v_{\alpha\beta}$ , and (bottom) estimated positive-sequence voltage in the fixed refer- |     |  |  |

|      | ence frame $\hat{v}^p_{\alpha\beta}$ .                                                       | 109 |  |  |

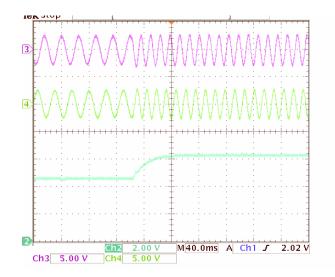

| 7.10 | Depicts the transient response of the proposed FRF-PLL to a utility fre-                     |     |  |  |

|      | aver av abor as from 40 Hz to 70 Hz (from ton to bottom) Desitive second                     |     |  |  |

quency change from 40 Hz to 70 Hz. (from top to bottom) Positive-sequence voltage  $v_{\alpha}$ , positive-sequence voltage  $v_{\beta}$ , and estimated angular frequency  $\hat{\omega}$ . 110 Depicts the transient response of the proposed EPE PLL to a utility free

7.11 Depicts the transient response of the proposed FRF-PLL to a utility frequency change from 70 Hz to 40 Hz. (from top to bottom) Positive-sequence voltage  $v_{\alpha}$ , positive-sequence voltage  $v_{\beta}$ , and estimated angular frequency  $\hat{\omega}$ . 110 List of figures

# Chapter 1

# Introduction

Since the emergence of the first semiconductor device, the evolution of electronics has become an unquestioned reality. It is evident that the development of electronic equipment has significantly changed patterns of behavior of individuals and has substantially improved the quality of life. The great challenge that Electrical Engineering is facing at the beginning of this new millennium is to guarantee an operation of the power systems with the highest quality as demanded by different loads. To achieve this goal, the power electronics is playing an important role in the design and construction of equipment able to correct the distortions typical of a normal power system; thus improving the quality with which the Electricity is delivered to the load.

The important criterion, which makes the power electronics solutions unique, is that they are fundamentally multifunctionals, and can provide not only their main interfacing function, but also various utility functions. The general trend in power electronic devices has been to switch power semiconductors at increased frequencies to minimize harmonics and reduce passive component sizes. There are several areas in which power electronics plays a vital role. The research areas of power electronics include:

- Converters for utility applications such as static var compensation, voltage sag support, HVDC distribution systems, large variable speed drives.

- ▷ Interfacing with distributed energy resources such as micro turbines, fuel cells, and solar cells.

- ▷ Harmonics, power quality, and power filter design.

- ▷ Hybrid electric vehicle (HEV) applications such as motor drives or dc-dc converters.

- ▷ Soft switching inverters and DC-DC converters.

- ▷ Areas like transportation and utility applications.

The points mentioned above constitute a challenge in the field of power electronics, and had contributed to the emergence of new semiconductor devices, new switching and control strategies, and new topologies.

In the last decades the pulse width modulated two-level converters have been the dominant topology in the low power and some selected medium power applications. There has been on-going research on these power converters and, as technology evolves and matures, various new trends and performance of power converters can be identified. Several important issues play a key role in these new trends. Factors like increasing the power density, improving performance, reducing the cost, and also increasing the VA ratings of the converter are considered. There are several ways in which these factors can be achieved, for instance, to increase the power density the switching losses must be reduced. This is obtained by using soft-switching techniques, efficient power devices, and improving the thermal management. Now, to increase the system performance, then it is required to reduce the total harmonic distortions, to reduce the EMI problems, and to improve the dynamic response of the system.

As the power demand continues to grow unceasingly, the converters power ratings should also increase. In case that the conventional two-level converters are used in these high power applications, then the rating of the devices has to increase considerably, that is, the blocking voltage rating, current rating, thermal management, and so on must be increased accordingly. Multilevel converters, in contrast, allow high power ratings of the converters but using low rating devices. Recently, the study of multilevel converters has become an attractive solution in medium and high power applications as the voltage stress of power semiconductors, voltage harmonics, and electromagnetic interferences can be reduced. One of the first topologies of multilevel converters was the neutral point clamped inverter topology proposed by Nabae et al. in 1981. These converters incorporate a topological structure that allows a desired output voltage to be synthesized from among a set of different voltage sources isolated or interconnected. Thus, by synthesizing the AC output voltage from several DC voltage levels, staircase waveforms are produced, which approach the sinusoidal waveform with low harmonic distortion, as shown in Fig. 1.1. Thanks to the reduction of low frequency harmonics from the AC voltage, the size of the AC inductances can be reduced as well. In addition, they allow to handle at least twice the voltage of a conventional converter, while using the same type of switching devices; that is, due to the series connection of semiconductors, it is possible to reach medium-high voltages with standard components. The multilevel converter can therefore be described as a voltage synthesizer.

Considering that m is the number of steps of the phase voltage with respect to the negative terminal of the inverter, then the number of steps in the voltage between two phases of the load k is

$$k = 2m + 1 \tag{1.1}$$

and the number of steps p in the phase voltage of a three-phase load in wye connection is

$$p = 2k - 1$$

(1.2)

There are several advantages of multilevel inverters such as

- ▷ Low manufacturing costs as low rating devices are used;

- ▷ Improved waveform quality as levels in the converter are increased;

- ▷ Compact modules and no transformer needed;

Figure 1.1: Synthesis of the output voltage in multilevel converters: **a**) two levels, **b**) three levels and **c**) n-levels.

- ▷ Better synthesizing of the output waveforms which reduces the output filters and the rating of the passive components;

- ▷ Many possible connections are available such as single-phase, three-phase, and multi phase connections;

- ▷ Low switching frequency yields high efficiency.

When series connected capacitors are used to divide the DC-link voltage, three-level inverters (multilevel converters in general) have a DC-link voltage problem due to the following reasons:

- ▷ Unequal capacitor values due to manufacture tolerances.

- ▷ Unequal loading of the capacitors due to unintended switching delays.

- ▷ Unequal loading of the capacitors due to nonlinear loads containing even order harmonics.

- ▷ Dead-time implementation, which is always necessary in voltage source converters.

- ▷ Transformer-secondary leakage inductance or voltage imbalance due to manufacturing tolerances.

- ▷ Unbalanced load due to imbalances between the phases of the three-phase load.

- ▷ Dynamic operating conditions such as acceleration or deceleration of a motor.

- ▷ Imbalances in the parameters of the power semiconductors switching devices.

The unique structure of multilevel voltage source inverters allows them to reach high voltages with low harmonics without the use of transformers. This makes these unique power electronics topologies suitable for flexible AC transmission systems (FACTS) and custom power applications. The use of a multilevel converter to control the frequency, voltage output, phase angle, and active and reactive power flow at a DC/AC interface provides significant opportunities in the control of distributed power systems.

Additional applications of multilevel converters include adjustable speed motor drives, static var compensation, dynamic voltage restoration, harmonic filtering; or for a high voltage DC backtoback converter. As distributed power sources are expected to become increasingly prevalent in the near future, the use of a multilevel converter to control the frequency and voltage output (including phase angle) from renewable energy sources will provide significant advantages because of its fast response and autonomous control. Additionally, multilevel converters can also control the active and reactive power flow from a renewable energy source connected to the utility. If a capacitance is connected in parallel to the renewable energy source, then a multilevel converter can provide static var compensation even when there is no output power from the photovoltaic or fuel cell energy source. If banks of batteries or large capacitors are on the DC bus, then a multilevel converter can provide significant ridethrough capability for voltage sags or load swings experienced at the utility interface connection.

Multilevel inverters can operate not only with PWM techniques but also with amplitude modulation (AM), improving significantly the quality of the output voltage waveform. With the use of amplitude modulation, low frequency voltage harmonics are perfectly eliminated, generating almost perfect sinusoidal waveforms, with a THD lower than five percent. Another important characteristic is that each device can be operated at a low switching frequency, reducing the semiconductor stresses, and therefore reducing the switching losses.

### **1.1 Topologies of multilevel converters**

Up to now, the topologies for high power multilevel converter are classified in three main types: flying capacitor converter (FC), diode clamped converter (NPC) and cascaded H-bridge converter (HB).

A three-level diode-clamped inverter (NPC) is shown in Fig.1.2. In this circuit, the dcbus voltage is split into three levels by two series-connected bulk capacitors, C1 and C2. The middle point of the two capacitors n can be defined as the neutral point. The output voltage has three states:  $V_{dc}/2$ , 0, and  $-V_{dc}/2$ . For voltage level  $V_{dc}/2$ , switches S1 and S2 need to be turned on while the rest is maintained off; for  $-V_{dc}/2$ , switches S3 and S4 need to be turned on; and for the 0 level, S2 and S3 need to be turned on. The key components that distinguish this circuit from a conventional two-level inverter are diodes D1 and D2. These two diodes clamp the switch voltage to half the level of the dc-bus voltage. When both S1 and S2 turn on, the voltage across a and 0 is  $V_{dc}$ , i.e.,  $v_{a0} = V_{dc}$ . In this case, D2 balances out the voltage sharing between S3 and S4 with S3 blocking the voltage across C1 and S4 blocking the voltage across C2. Notice that output voltage  $v_{aN}$  is ac, and  $v_{a0}$  is dc. The difference between  $v_{aN}$  and  $v_{a0}$  is the voltage across C2, which is  $V_{dc}/2$ . If the output is removed out between a and 0, then the circuit becomes a dc/dc converter, which has three output voltage levels:  $V_{dc}$ ,  $V_{dc}/2$ , and 0.

Figure 1.2: Neutral Point Clamped (NPC) multilevel converter.

Figure 1.3 illustrates the fundamental building block of a phase-leg capacitor-clamped inverter (FC). The circuit has been called the flying capacitor inverter [1], [5], [6] with independent capacitors clamping the device voltage to one capacitor voltage level. The inverter in Fig.1.3 provides a three-level output across a and N, i.e.,  $v_{aN} = V_{dc}/2$ , 0, or  $-V_{dc}/2$ . For voltage level  $V_{dc}/2$ , switches S1 and S2 need to be turned on; for  $-V_{dc}/2$ , switches S3 and S4 need to be turned on; and for the 0 level, either pair (S1, S3) or (S2, S4) needs to be turned on. Clamping capacitor C1 is charged when S1 and S3 are turned on, and is discharged when S2 and S4 are turned on. The charge of C1 can be balanced by proper selection of the 0-level switch combination.

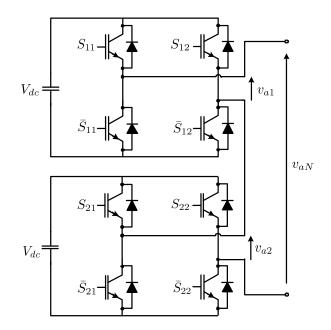

A different converter topology which is based on the series connection of single-phase H-bridge inverters (HB) with separate dc sources is shown in Fig.1.4. This figure shows the power circuit for one phase leg of a five-level inverter with two cells in each phase. The resulting phase voltage is synthesized by the addition of the voltages generated by the different cells. Each single-phase full-bridge inverter generates three voltages at the output:  $+V_{dc}$ , 0, and  $-V_{dc}$ . This is made possible by connecting the capacitors sequentially to the ac side via the four power switches. The resulting output ac voltage swings from  $-2V_{dc}$  to  $2V_{dc}$  with five levels, and the staircase waveform is nearly sinusoidal, even without filtering.

Other topologies can be found in the literature of power and industrial electronics, which are often a combination of the three basic topologies or modifications of them. They can be found under the following names:

▷ Asymmetric Hybrid Multilevel Cells.

Figure 1.3: Flying capacitor (FC) multilevel converter.

Figure 1.4: H-bridge (HB) multilevel converter.

- ▷ Mixed-Level Hybrid Multilevel Cells.

- ▷ Soft-Switched Multilevel Inverters.

- ▷ Matrix converters.

- ▷ Transformer-coupled inverters.

- ▷ Diode/capacitor clamped converters.

- ▷ New diode clamped multilevel converters.

### **1.2** Classification of Modulation Strategies

The modulation methods used in multilevel inverters can be classified according to switching frequency as fundamental switching frequency and high switching frequency PWM. Methods that work with high switching frequencies have many commutations for the power semiconductors in one period of the fundamental output voltage. A very popular method in industrial applications is the classical carrier-based sinusoidal PWM (SPWM) that uses the phase-shifting technique to reduce the harmonics in the load voltage [1], [2], [3]. Another interesting alternative is the SVM strategy, which has been used in three-level inverters [4].

Methods that work with low switching frequencies generally perform one or two commutations of the power semiconductors during one cycle of the output voltages, generating a staircase waveform. Representatives of this family are the multilevel selective harmonic elimination [5], [6] and the space-vector control (SVC) [7]. Some of the most important modulation techniques are listed below:

- Multilevel SPWM. Several multicarrier techniques have been developed to reduce the distortion in multilevel inverters, based on the classical SPWM with triangular carriers. Some methods use carrier disposition and others use phase shifting of multiple carrier signals [2], [8], [9].

- SVM technique. It can be easily extended to all multilevel inverters [10]-[16]. These vector diagrams are universal regardless of the type of multilevel inverter. In other words, the modulation is valid for five-level diode-clamped, capacitor-clamped, or cascaded inverter. Space-vector PWM methods generally have the following features: good utilization of dc-link voltage, low current ripple, and relatively easy hardware implementation by a digital signal processor (DSP). These features make it suitable for high-voltage high-power applications. However, as the number of levels increases, redundant switching states and the complexity of selecting switching states increase dramatically.

- ▷ Selective Harmonic Elimination. To minimize harmonic distortion and to achieve adjustable amplitude of the fundamental component, up to m 1 harmonic contents can be removed from the voltage waveform. In general, the most significant low-frequency harmonics are chosen for elimination by properly selecting angles among different level inverters, and high-frequency harmonic components can be readily removed by using additional filter circuits.

- SVC. A conceptually different control method for multilevel inverters, based on the space-vector theory, has been introduced [17]. This control strategy, called SVC, works with low switching frequencies and does not generate the mean value of the desired load voltage in every switching interval, as is the principle of SVM. The main idea in SVC is to deliver to the load a voltage vector that minimizes the space error or distance to the reference vector. This method is simple and attractive for high number of levels. As the number of levels decreases, the error in terms of the generated vectors with respect to the reference will be higher; this will increase the load current ripple.

- Direct Torque Control (DTC). This technique has been developed for low-voltage two level inverters as an alternative to the field oriented method to effectively control torque and flux in AC drives [18]. DTC and hysteresis current control techniques have also been applied in multilevel inverters [19]. It must be noticed that one major manufacturer has been selling medium-voltage three-level diode clamped inverters controlled with DTC [20].

### **1.3** Phase locked-loop algorithms

One crucial aspect in the control of grid-connected power converters, is the detection of the fundamental-frequency positive-sequence component of the utility voltage under unbalanced and distorted conditions. Specifically, the detection of the positive-sequence voltage component at fundamental frequency is essential for the control of distributed generation and storage systems, flexible AC transmission systems (FACTS), power line conditioners and uninterruptible power supplies (UPS). The most widely accepted solution to provided this synchronization are the phase-locked loop (PLL) based technics. The basic PLL concept has been known and widely utilized since it was first proposed in 1922. From that time, PLLs have been used in instrumentation, space telemetry, and many other applications requiring a high degree of noise immunity and narrow bandwidth.

A phase-locked loop (PLL) is a system that generates an alternating signal whose phase shift and frequency are equal to those of a "reference" signal. In general, a conventional PLL comprises a phase frequency detector (PFD) aimed to detect phase error and frequency error between the sensed input signal and an internally reconstructed signal. This error signal is processed in a filter and the result is used to adjust the frequency of a voltage controlled oscillator (VCO). A PLL circuit responds to both the frequency and the phase shift of the input signal. It may automatically increase or decrease the frequency of a controlled oscillator until its output signal matches both frequency and phase shift of the reference. The PLL scheme compares its output phase with the phase of an incoming reference signal and adjusts itself until both are aligned, i.e., the PLL output's phase is "locked" to that of the input signals is very close to zero) the frequency of the output signal is a multiple (integer or fractional) of the input signal's frequency.

One of the most common implementations of integrated circuits' PLLs is in frequency synthesizers, where PLLs are used to generate a set of programmable frequencies. Applications of frequency synthesizers include LO (Local Oscillator) for up- and down- conversion in wireless communications systems ( such as cell phones), demodulation of both FM and

AM signals, recovery of clock timing information in a data stream (such as those made available in a disk drive), and clock multipliers in microprocessors. In wireless communications ICs, PLLs have to achieve key performance metrics of various parameters, including phase noise, spur levels, and lock time, which tend to trade off with each other and hence challenge IC designers everywhere. Given the widespread use of PLLs and their complexity, a lot of research effort has been applied to the understanding of PLLs and simulation techniques that can facilitate their implementation in ICs.

One crucial aspect in the control of grid-connected power converters is the detection of the fundamental-frequency under distorted conditions. In particular, in three-phase systems, it is necessary to detect the positive-sequence component of the utility voltage under unbalanced and distorted conditions. The PLL schemes have been used in power electronics systems which require grid voltage information, such as the frequency, phase angle and amplitude. They are in fact the most widely accepted solution to provide synchronization with the grid. The detection and synchronization to the fundamental component is essential for the control of distributed generation and storage systems, flexible ac transmission systems (FACTS), power line conditioners and uninterruptible power supplies (UPS).

### **1.4** Objectives, structure and main contributions

The objectives of this thesis can be summarized as follows:

*[First]*: to establish mathematical models based on differential equations for the different topologies of multilevel converters. The hypothesis is that with a correct description of the dynamics of the systems, is possible to design a control law that would maximize the characteristics of the system under study.

*[Second]*: based on the mathematical models proposed, design an appropriated control law in order to obtain the most benefits of the systems. The main reason of design the control law in base of the model is try to identify the control input (or inputs) that permits the balance of the capacitor voltages, which is the most important problem with the multilevel converter systems.

[*Third*]: validate the mathematical models and the control laws with simulations results and/or experimental results.

*[Fourth]*: demonstrate that with a complete description of the source voltage, is possible to design a PLL algorithm to perform properly under unbalanced conditions, and to be robust against angular frequency variations, also robust against harmonic distortion present in the source voltage signal.

[*Fifth*]: validate the proposed PLL algorithms with simulation results and/or experimental results.

The thesis is structured as follows:

Chapter 2 presents a model describing the dynamics of a three level neutral point clamped converter used in a synchronous rectifier application. The highly nonlinear model, originally in *abc*-coordinates, is also expressed in its  $\alpha\beta\gamma$ -coordinates. Special attention is given to the  $\gamma$ -component of the control input, which represents a degree of freedom crucial for the balancing of the capacitors voltages.

Unlike others models presented in the literature [71], [75] that are more analytical models

describing the basic operation of the converter or the effects of the systems parameters, the proposed model is an average model working with continuous signals. This is true if the switching frequency is much faster than the nominal frequency, in this case, 50 or 60 Hz; then considering systems working with a switching frequency of 10 KHz, the assumption is correct. This means that the inputs of the model are the duty ratios instead of the switching sequence. Moreover, the proposed model is presented in  $\alpha\beta\gamma$ -coordinates, or fixed reference frame, instead of the rotating reference frame by using a combination of Clarke's and Park's transformations [73], [74], this is traduced in a minor computational requirements, and also, it is not required the knowledged of the angular frequency for the calculation of the reactive power and the instant power. It is also important to clarify that the proposed model represents the dynamics of the converter and is not an study with design purpose of the parameters of the converter [76]. The parameters of the converter are expressed in the model, but there are considered as an unknown constants.

Chapter 3 presents an adaptive controller for a synchronous rectifier using a three level NPC. The controller guarantees regulation and balance of the output capacitors voltages, as well as a close to unity power factor, simultaneously. The design is based on the model in  $\alpha\beta\gamma$ -coordinates of the three level converter above proposed. Special attention is given to the  $\gamma$ -component of the control input, since it has direct influence in the balancing of the capacitors voltages, represented here as the arithmetic difference of voltages.

Unlike other techniques of control [4], [72], [70], where are focused in obtaining the best switching sequence to solve the problems of balancing the voltages of the capacitors and harmonic elimination, based in analytical models, the proposed controller is based in a mathematical model, in this case, an average continuous model. This allow to obtain the proper duty ratios for the switching sequence and for the implementation it is necessary a correct modulation scheme, in this case it was implemented the proposed in [24].

Chapter 4 presents the modeling and control process of the cascade h-bridge single-phase multilevel converter used as an active filter. Based on the model, a controller is proposed to guarantee a current tracking of the line current towards a reference proportional to the line voltage. Simultaneously, the controller guarantees the regulations and balance of the capacitor voltages.

Chapter 5 presents the modeling and control process of the cascade H-bridge three-phase multilevel converter used as a shunt active filter. Based on the model, a controller is proposed to compensate harmonic distortion and reactive power due to a nonlinear load. Simultaneously, the controller guarantees the regulations and balance of the capacitor voltages. The results are shown for a cascade H-bridge three-phase five-level converter, however, all results can be easily extended to higher levels.

Chapter 6 presents the design and implementation of a single phase PLL based on an adaptive observer. The algorithm assumes that the signal is produced by a harmonic oscillator where the frequency is an unknown parameter, and only one of the states is available. A prototype has been built and experimental results are presented to asses its performance.

Chapter 7 presents a PLL which is able to provide an estimation of the angular frequency, and both the positive and negative sequences of the fundamental component of a three-phase signal. These sequences are provided in fixed reference frame coordinates, and thus the proposed algorithm is referred as fixed reference frame PLL (FRF-PLL). The FRF-PLL is intended to perform properly under severe unbalanced conditions, and to be robust against

angular frequency variations in the three-phase source voltage signal. Although not considered in the design, it is shown that the scheme is also robust against harmonic distortion present in the source voltage signal.

Finally, the concluding remarks, the scientific production and the future work.

# **Chapter 2**

# **NPC Multilevel Converter: Mathematical Model**

### 2.1 Introduction

Among the various multilevel converters, the NPC or Diode-Clamped topology is undoubtedly one of the most used and studied.

The advantages of the NPC topology are:

- ▷ The lock voltage of one semiconductor device is a single voltage input of one capacitor,  $V_{pn}/(n-1)$  in the case of n levels.

- ▷ The number of capacitors required is small compared with other multilevel topologies. This point is especially interesting since they are components reagents which entail a higher cost in the converter.

- ▷ Can be connected directly to a DC bus, without adding other additional capacitors.

- ▷ Does not require transformers.

- ▷ Change from one state to another via actuation of a single switch.

This topology presents, however, the followings drawbacks:

- ▷ The fixing diodes or clamping diodes must be chosen capable to driving the nominal current of the converter. This requirement must be considered seriously in the design of the converter.

- ▷ In topologies with more than three levels, it is required that the clamping diodes block different voltages depending on their position in the converter.

- ▷ It is necessary that the tensions of the capacitors remain balanced in any point of work, complicating the control system of the converter. The balancing of the voltages of capacitors is difficult as it is increasing the number of levels of the converter, it can even be impossible in some operating conditions.

In general, the provided advantages of NPC converters make interesting the task to develop a complete mathematical model of the converter in order to allow the design of more adequate control strategies.

This chapter presents a model that describes the dynamics of a three level neutral point clamped converter used in a synchronous rectifier application. The highly nonlinear model, originally in *abc*-coordinates, is also expressed in its  $\alpha\beta\gamma$ -coordinates. Special attention is given to the  $\gamma$ -component of the control input, which represents a degree of freedom crucial for the balancing of the capacitors voltages. It is shown that the arithmetic difference and sum of the capacitors voltages are two natural states of the system and, indeed, they reduce considerably the model expressions. It is also shown that the controller  $\gamma$ -component has a minimum influence on the sum of the capacitors voltages, but it has a strong influence on the difference, hence its importance in the capacitor voltage balance. Simulations are presented to validate the proposed model.

### 2.2 Model of the three level NPC inverter

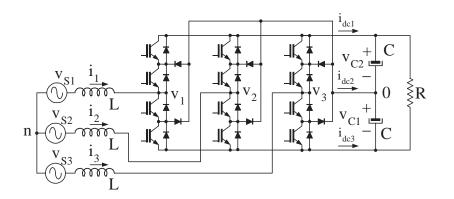

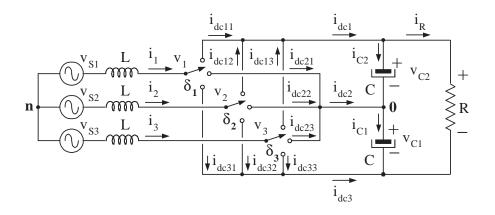

The basic setup for the synchronous rectifier application using a three level NPC inverter discussed in this chapter is shown in Fig. 2.1, and the equivalent circuit with ideal switches is shown in Fig. 2.2.

Figure 2.1: Synchronous rectifier based on a three level NPC inverter.

The modeling process is divided in two stages. In the first stage, we obtain the expressions for the inductor current dynamics, and second, we obtain the expressions to describe the dynamics of the capacitor voltages. Some approximations are proposed to reduce the complexity of such expressions. We note that a natural description of the capacitors voltages dynamics consists in considering, as controlled variables, the addition and the difference of both capacitors voltages. We conclude this section by presenting the transformation of the proposed model from *abc*-coordinates to  $\alpha\beta\gamma$ -coordinates where we introduce the third coordinate  $\gamma$  to consider the third degree of freedom available in the input control. This control component is crucial in the balancing of the capacitors voltages as it will become clear later.

Figure 2.2: Synchronous rectifier equivalent circuit based on a three level inverter with ideal switches.

### 2.2.1 The inductors current dynamics

Direct application of Kirchhoff's Voltage Law (KVL) yields

$$v_{S1} = L\frac{di_1}{dt} + v_1 + v_{0n}$$

$$v_{S2} = L\frac{di_2}{dt} + v_2 + v_{0n}$$

$$v_{S3} = L\frac{di_3}{dt} + v_3 + v_{0n}$$

(2.1)

where

| $v_{S1}, v_{S2}, v_{S2}$      | : | source voltages referred to "n"    |

|-------------------------------|---|------------------------------------|

| $i_1,  i_2,  i_3$             | : | inductor currents                  |